# AN INVESTIGATION INTO THE FAIL SAFENESS OF SAFETY CRITICAL INSTRUMENTATION AND CONTROL IN A SODIUM COOLED FAST REACTOR

By

## SRIKANTAM SRAVANTHI

(Enrollment No: ENGG02201204006)

## INDIRA GANDHI CENTRE FOR ATOMIC RESEARCH KALPAKKAM

A thesis submitted to the

Board of Studies in Engineering Sciences

In partial fulfillment of requirements

For the Degree of

## **DOCTOR OF PHILOSOPHY**

of

## HOMI BHABHA NATIONAL INSTITUTE

February, 2018.

## Homi Bhabha National Institute

## Recommendations of the Viva Voce Committee

As members of the Viva Voce Board, we certify that we have read the dissertation prepared by Ms. Srikantam Sravanthi entitled "An investigation into the fail safeness of safety critical instrumentation & control in a sodium cooled fast reactor" and recommend that it may be accepted as fulfilling the dissertation requirement for the Degree of Doctor of Philosophy.

| £                              | 21/1                        |       |            |

|--------------------------------|-----------------------------|-------|------------|

| Chairman: Dr. M. Sai Baba      | Dean Academir<br>(Engg Sci) | Date: | 26/2/2018  |

| Guide / Convener: Dr. K. Devan |                             | Date: | 26/2/2018  |

| Examiner: Prof. V. N. Achurcho | Neikan Pris                 | Date: | 26/02/2018 |

| Member 1- Dr. B.P.C. Rao       |                             | Date: | 26/2/2018  |

|                                | Konte                       |       | 26.62.2018 |

| Member 2- Dr. Gopika Vinod     | 9 "                         | Date: |            |

Final approval and acceptance of this thesis is contingent upon the candidate's submission of the final copies of the dissertation to HBNI.

I hereby certify that I have read this thesis prepared under my direction and recommend that it may be accepted as fulfilling the dissertation requirement.

Date:

Place: Indira Gandhi Centre for Atomic Research (IGCAR)

Kalpakkam

Dr. K. Devan 26/2/2018-

STATEMENT BY AUTHOR

This dissertation has been submitted in partial fulfillment of requirements for an advanced

degree at Homi Bhabha National Institute (HBNI) and is deposited in the Library to be made

available to borrowers under rules of the HBNI.

Brief quotations from this dissertation are allowable without special permission, provided that

accurate acknowledgement of source is made. Requests for permission for extended quotation

from or reproduction of this manuscript in whole or in part may be granted by the Competent

Authority of HBNI when in his or her judgment the proposed use of the material is in the

interests of scholarship. In all other instances, however, permission must be obtained from the

author.

Date:

Place: Kalpakkam

(Srikantam Sravanthi)

S. Saavanthi

## **DECLARATION**

I, hereby declare that the investigation presented in the thesis has been carried out by me. The work is original and has not been submitted earlier as a whole or in part for a degree / diploma at this or any other Institution / University.

Date:

Place: Kalpakkam

(Srikantam Sravanthi)

S. Saavanthi

## List of publications arising from the thesis

## **JOURNALS**

- S. Sravanthi, R. Dheenadhayalan, M. Sakthivel, K. Devan, K. Madhusoodanan, A Method for Online Diagnostics of Electromagnetic Relays Against Contact Welding for Safety Critical Applications in *IEEE Transactions on Components, Packaging and Manufacturing* Technology, vol. 5, issue 12, pp. 1734-1739, Dec. 2015.

- 2. **S. Sravanthi**, R. Dheenadhayalan, K. Devan, K. Madhusoodanan, An Inherently Fail-Safe Electronic Logic Design for a Safety Application in Nuclear Power Plant *in Process Safety and Environmental Protection*, vol. 111, issue C, pp. 232-243, 2017.

- 3. **S. Sravanthi,** R. Dheenadhayalan, K. Madhusoodanan, K. Devan, Safety Criteria and Dependability management practices: A case study with I&C systems of Prototype Fast Breeder Reactor *in Nuclear Technology*, vol. 201, pp. 180-189, Feb. 2018.

## **CONFERENCE PUBLICATION**

1. **S. Sravanthi**, R. Dheenadhayalan, Gopika Vinod, K. Madhusoodanan, K. Devan, Reliability model of a relay output card with diagnostic circuitry for safety instrumented system, in proceedings of the *IEEE conference on System Reliability and Science*, Paris, France, pp. 130-136, 2016. (DOI:10.1109/ICSRS.2016.7815851).

## **CONFERENCES**

S. Sravanthi, R. Dheenadhayalan, K.Madhusoodanan, A method for Prognostics in Electromagnetic relay for reliability improvement in a safety critical nuclear application in International *Applied Reliability Symposium*, Chennai, Tamilnadu, Aug. 19-21, 2015. 2. **S. Sravanthi**, R. Dheenadhayalan, M. Sakthivel, SLN. Swamy, K. Madhusoodanan, Life Testing of Power Contactors in 2<sup>nd</sup> *SRESA National conference on Reliability and Safety Engineering*, Chennai, Tamilnadu, Oct. 8-10, 2015.

S. Saavanthi.

(Srikantam Sravanthi)

## DEDICATED TO MY PARENTS

#### **ACKNOWLEDGEMENTS**

I take this opportunity to express my gratitude to the people who have been very helpful to me in carrying out my research work and accomplishing the thesis.

First and foremost I acknowledge Shri.R. Dheenadhayalan, SO/E, EIG, IGCAR for his persistent encouragement, constant motivation, everlasting patience and insightful guidance in all the ways leading to the completion of my Ph.D work. The joy and enthusiasm he has for this research was contagious and motivational for me, even during tough times.

I sincerely thank my technology adviser Shri. K.Madhusoodanan, former group director, EIG, IGCAR and research supervisor Dr. K. Devan, Head, Reactor Neutronics Division, Reactor Design Group, IGCAR for valuable guidance and support. I convey my heartiest appreciation to my doctoral committee Chairman Dr. M. Sai Baba and committee members Dr. B.P.C. Rao and Dr. Gopika Vinod for their support and encouragement during my research work.

My sincere gratitude to, Dr. A.K. Bhaduri, Director, IGCAR and Dr. S.A.V. Satya Murty, Dr. P.R. Vasudeva Rao and Shri S.C. Chetal, former Directors, IGCAR for providing excellent environment to carry out research work.

My special thanks to Shri. A.Venkatesan Head ICD, Shri.M. Manimaran Head PIS, Ms. Somavathi, Mrs. Varuna, Mr. Pradeesh, Mr. Ananda Kumar, Mr. SLN. Swamy, Mrs. Nisha, Mr. Ankit, Mr. Subramanian, Mr. G.K. Mishra, Mr.C.P.Nagaraj, Mr.M. Saktivel, Mr. Raj Kumar and all members of ICD for their support and creating a homely environment at the work place during this period.

I specially acknowledge EID Head/EID colleagues for the inputs on card details of computerbased systems and voting logics.

I am grateful for the financial support provided by research fellowship scheme from Indira Gandhi Centre for Atomic Research, Department of Atomic Energy for the duration of the work.

I thank HBNI, CICS and CSIR for providing the international travel grant to attend the 2016

International Conference on System Reliability and Science, Paris, France.

It is my pleasure to thank all my friends and seniors Prema, Sumathi.V, Rajasekar, Balaji,

Chandan Reddy, Shiva, Nagendra, Veerendra, Samba, Anand, Shivang, Santosh, Chandan

Kumar, Vipin, Naveen, Sumathi.G, Naseema, Preethi, Raghavendra, Balakrishnan, Sashwat,

Sanjay, Bubathi, Arun Babu, Anil, Priya, Vivek.

It has been a great honor for me to work in IGCAR and to be surrounded with some of the

brightest and loving people, I have met. To all, I say Thank you from the bottom of my heart.

Finally, I would like to thank my parents Smt.S. Sulochana, Shri.S. Ramachandraiah and my

siblings Mrs. Sreevani and Mrs. Sravani who have been the source of constant inspiration and

motivation for me throughout my life. My heart is filled with diligent gratitude to all my family

members who have created an ideal environment for me to smoothly handle my career and bring

the best out of me in all the endeavors in my life.

Thank you everyone.

(Srikantam Sravanthi)

## **CONTENTS**

| SY  | NOPSIS.  |          |                                                                 | i          |

|-----|----------|----------|-----------------------------------------------------------------|------------|

| LIS | ST OF FI | GURES.   |                                                                 | iv         |

| LIS | ST OF TA | ABLES    |                                                                 | vi         |

| LIS | ST OF AI | BBREVL   | ATIONS                                                          | vii        |

| 1   | INTRO    | DUCTIC   | )N                                                              |            |

|     | 1.1      | Backgr   | ound                                                            | 1          |

|     | 1.2      | An Ove   | erview of Instrumentation and Control Systems in a Nuclear Powe | er Plant 4 |

|     | 1.3      | Fail-saf | fe Design                                                       | 6          |

|     | 1.4      | Literatu | are Survey                                                      | 8          |

|     |          | 1.4.1    | Design principles to reduce probability of failure on demand    | 8          |

|     |          | 1.4.2    | Survey on design principles used in shutdown systems            | 14         |

|     | 1.5      | Researc  | ch Objectives                                                   | 17         |

|     | 1.6      | Organiz  | zation of the Thesis                                            | 20         |

| 2   | STUDY    | OF SAI   | FETY CRITICAL I&C SYSTEMS IN PFBR                               |            |

|     | 2.1      | Introdu  | ction                                                           | 22         |

|     | 2.2      | Shutdo   | wn System                                                       | 24         |

|     |          | 2.2.1    | Sensors                                                         | 24         |

|     |          | 2.2.2    | Signal processing.                                              | 27         |

|     |          | 2.2.3    | Actuation system                                                | 34         |

|     | 2.3      | Compu    | tter Based Systems used for Shutdown                            | 39         |

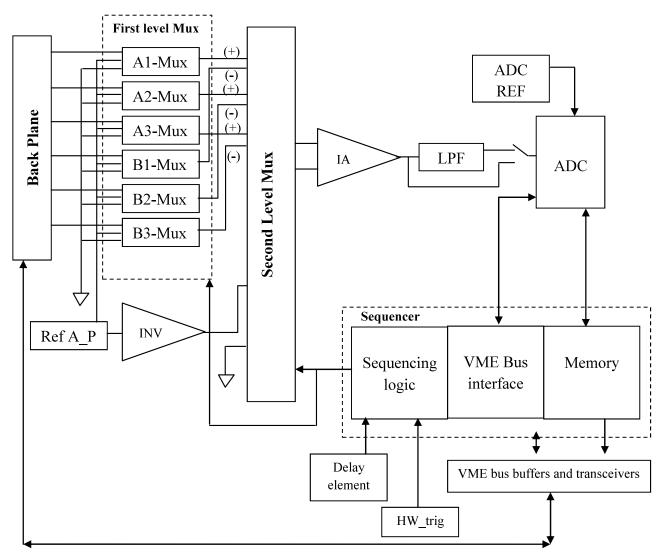

|     |          | 2.3.1    | Analog Input Card (AIC)                                         | 39         |

|     |          | 2.3.2    | Digital Input Card (DIC)                                        | 41         |

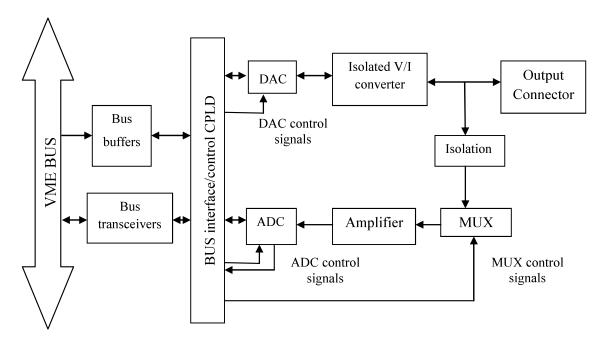

|     |          | 2.3.3    | Analog Output Card (AOC)                                        | 42         |

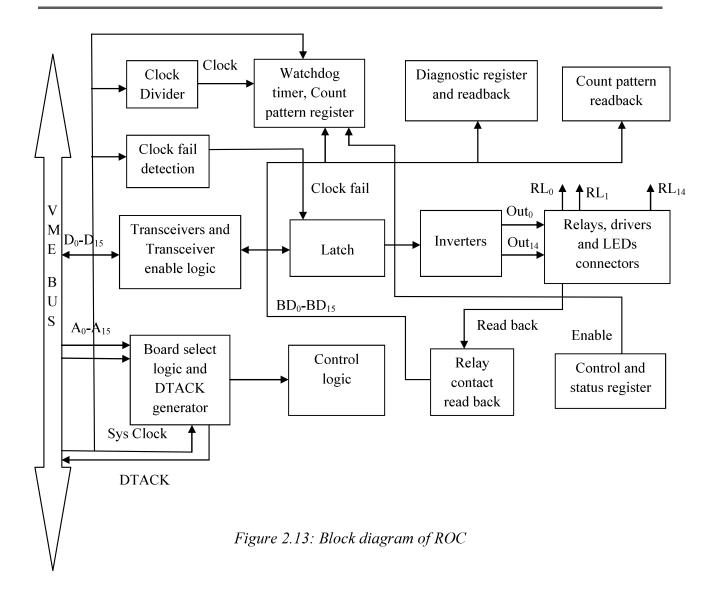

|     |          | 2.3.4    | Relay Output Card (ROC)                                         | 44         |

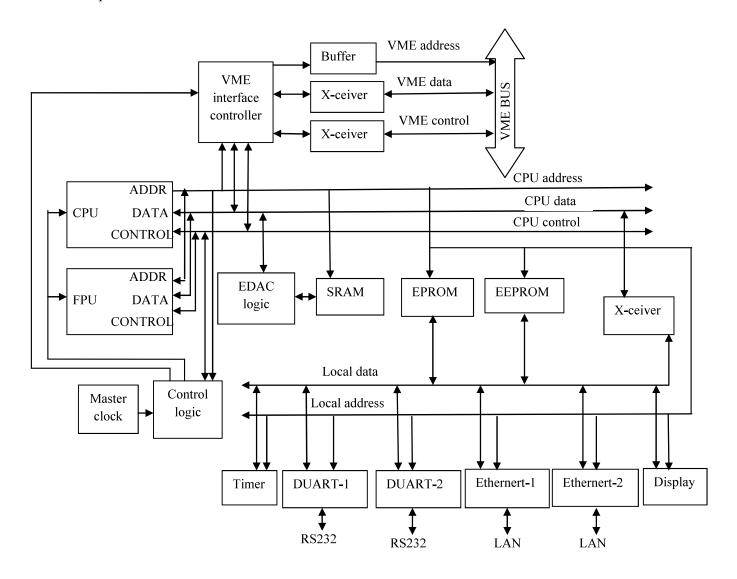

|     |          | 2.3.5    | Central Processing Unit card (CPU)                              | 46         |

|     | 2.4      | Decay 1  | Heat Removal System                                             | 48         |

|     | 2.5      | Summa    | nry                                                             | 51         |

| 3   | A NOV    | EL ONL   | INE DIAGNOSTICS OF EM RELAYS AGAINST CONTACT                    | WELD       |

|     | 3.1      | Introdu  | ction                                                           | 52         |

|     |          | 3.1.1    | Electromagnetic relay.                                          | 52         |

|   |         | 3.1.2   | Failure modes of EM relay                                            | 53    |

|---|---------|---------|----------------------------------------------------------------------|-------|

|   |         | 3.1.3   | Arc and its consequences                                             | 55    |

|   | 3.2     | Weldin  | g Concerns in Nuclear Power Plant                                    | 59    |

|   | 3.3     | A Meth  | nod for Online Diagnostics of EM Relay                               | 61    |

|   |         | 3.3.1   | Fundamental principle                                                | 61    |

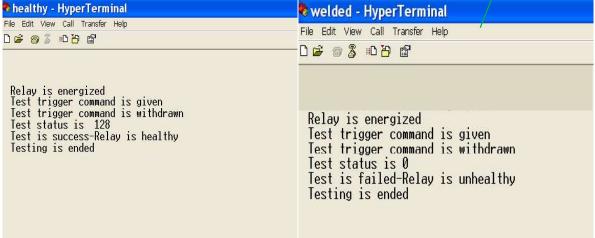

|   |         | 3.3.2   | Verification of proposed method                                      | 62    |

|   |         | 3.3.3   | Results                                                              | 65    |

|   |         | 3.3.4   | Reliability improvement                                              | 67    |

|   |         | 3.3.5   | Limitations and precautions                                          | 67    |

|   | 3.4     | Summa   | ıry                                                                  | 68    |

| 4 |         |         | PUT CARD WITH WELD DIAGNOSTICS AND RELIABILITY                       |       |

| M | ODELLIN | . –     |                                                                      |       |

|   | 4.1     | _       | Output Card with Diagnostics                                         |       |

|   |         | 4.1.1   | Implementation                                                       |       |

|   |         | 4.1.2   | Experimental setup                                                   |       |

|   | 4.2     |         | lity Analysis                                                        |       |

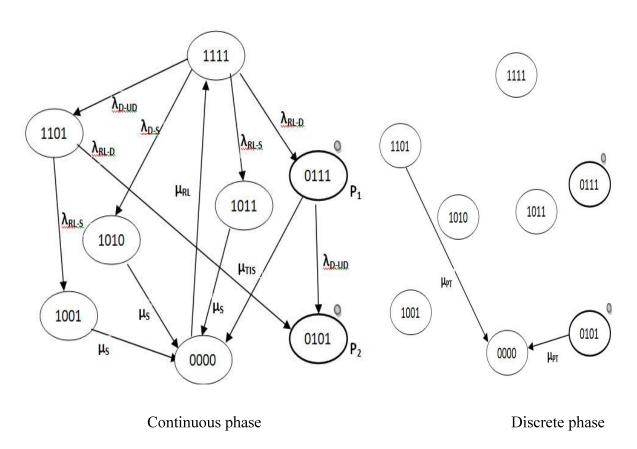

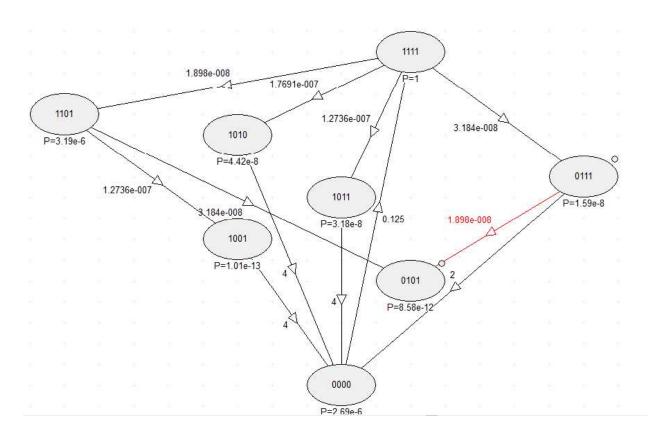

|   |         | 4.2.1   | Markov model of the system                                           |       |

|   |         | 4.2.2   | Failure rate calculation                                             |       |

|   |         | 4.2.3   | Markov analysis of the ROC                                           |       |

|   |         | 4.2.4   | Sensitivity analysis                                                 |       |

|   | 4.3     |         | ary                                                                  |       |

| 5 | ELECT   | ROMAC   | GNETIC CONTACTORS: LIFE TESTING AND FAILURE ANALY                    | YSIS  |

|   | 5.1     | Introdu | ction                                                                | 89    |

|   | 5.2     | Reliabi | lity Demonstration Testing using Test of Hypothesis Technique        | 90    |

|   | 5.3     | RDT P   | lan for a EM contactor: Application in PFBR                          | 92    |

|   |         | 5.3.1   | Test setup                                                           | 93    |

|   |         | 5.3.2   | Test results                                                         | 96    |

|   | 5.4     | Failure | Analysis                                                             | 96    |

|   |         | 5.4.1   | Field driver relay                                                   | 96    |

|   |         | 5.4.2   | EM Contactors                                                        | 98    |

|   | 5.5     | Summa   | ary                                                                  | 102   |

| 6 | INHER   | ENT FA  | IL-SAFE CIRCUITS TO IMPROVE FAIL-SAFE DESIGN                         |       |

|   | 6.1     | Inheren | nt Fail-safe Design: An approach to Probability of Failure on Demand | d 103 |

|    | 6.2     | Fail-safe AND Gate |                                                               |           |

|----|---------|--------------------|---------------------------------------------------------------|-----------|

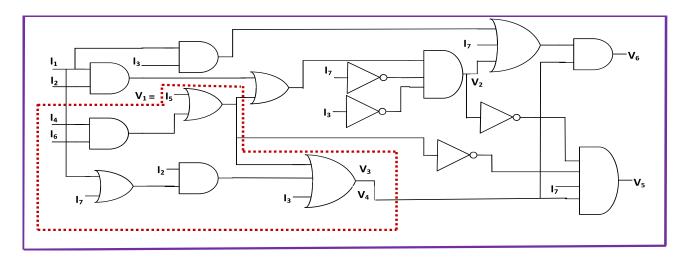

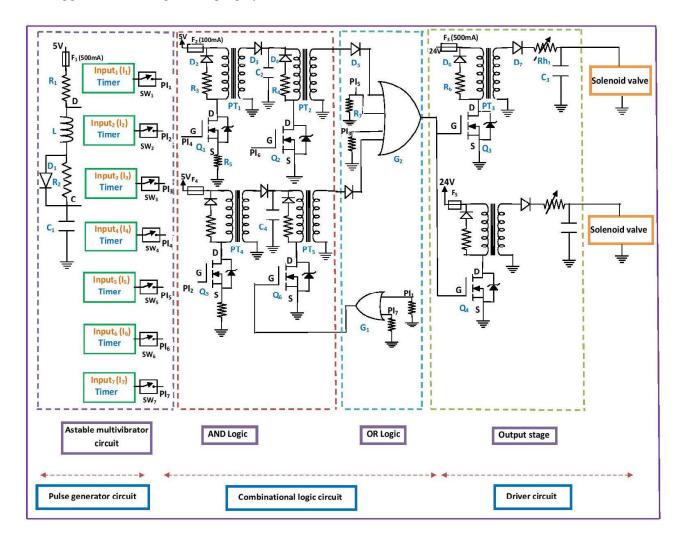

|    | 6.3     | Inheren            | ntly Fail-safe Pulsating Logic Design for PFBR Safety Grade D | ecay Heat |

|    | Rem     | oval Circ          | euit                                                          | 107       |

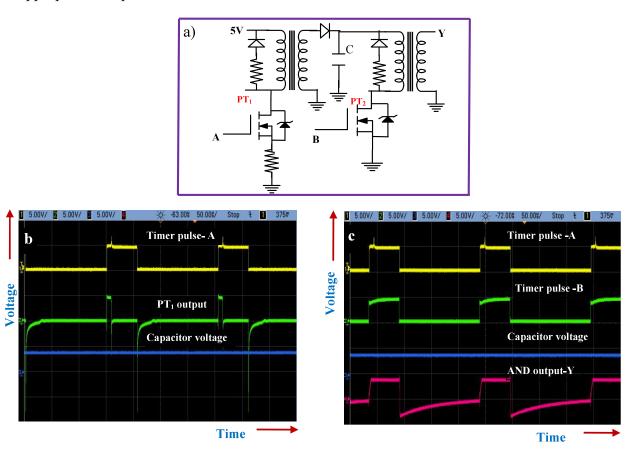

|    |         | 6.3.1              | Inherently fail-safe pulsating logic design                   | 109       |

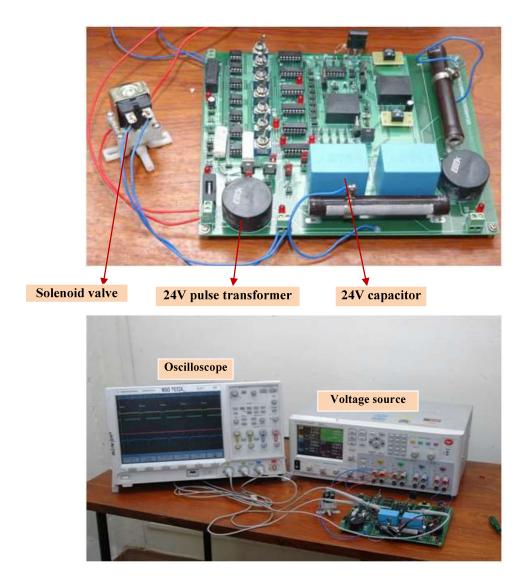

|    |         | 6.3.2              | Experimental Verification                                     | 112       |

|    |         | 6.3.3              | Results                                                       | 112       |

|    |         | 6.3.4              | Failure mode effect analysis verification                     | 114       |

|    |         | 6.3.5              | Unsafe failure probability on demand                          | 123       |

|    |         | 6.3.6              | Precautions and possible improvements                         | 127       |

|    | 6.4     | Applica            | ations of Inherent Fail-safe Circuit                          | 128       |

|    | 6.5     | Summa              | ary                                                           | 129       |

| 7  | SUMM    | ARY AN             | ND SCOPE FOR FUTURE WORK                                      | 130       |

|    | 7.1     | Summa              | ary                                                           | 130       |

|    | 7.2     | Future             | Work                                                          | 134       |

| RE | EFERENC | ES                 |                                                               | 135       |

|    |         |                    |                                                               |           |

## **SYNOPSIS**

Nuclear power plants (NPPs) are intended to achieve the safety margins and high reliability of design features. Instrumentation and Control (I&C) systems are very crucial to achieve the desired safety function of various systems in a NPP. The stringent reliability requirements are achieved by adopting various measures like defense in depth, redundancy, independence, periodic surveillance and fail-safe design. "Fail-safe" behavior is the capability of any system to reach predefined safe state in the event of malfunction of components.

Prototype Fast Breeder Reactor (PFBR) is a sodium cooled Fast Breeder reactor Indira Gandhi Centre for Atomic Research and is being commissioned at Kalpakkam, as a part of India's second stage nuclear energy programme. The research problem is to perform a review of the current practices, assumptions and techniques followed in design of I&C systems in a fast reactor towards achieving a fail-safe design and come out with relevant solutions for further improvement. The present study focuses on ensuring failure free performance of shutdown system and decay heat removal system. I&C for shutdown systems are to be designed "fail-safe" so that any fault in sensors, logic processors or final control elements will lead to shutdown of the reactor. Similarly, systems for decay heat removal should ensure timely initiation and sustenance of decay heat removal after reactor shutdown. Any fault in such systems should initiate unintended decay heat removal even if it leads to loss of power rather than failure to initiate safety action.

Average Probability of Failure on Demand (PFD<sub>Avg</sub>) is the quantitative parameter of interest to the safety systems considered for this study. The study of self-diagnostics and fail-safe design plays an important role in the overall goal of PFD<sub>Avg</sub>. Self-diagnostics helps in detecting dangerous failure. With the aid of fail-safe design, in case of dangerous detected failures, system

can be taken to fail-safe state. Further, the system design must ensure that all detected faults lead to fail-safe state.

The quantitative effect of each of the design principle such as redundancy, independence, diversity, periodic surveillance and fail-safe design on the  $PFD_{Avg}$  is studied in this thesis. The general design principles used in a typical shutdown system and decay heat removal system are studied. From review of various design modules used in PFBR, the proposed novel solutions for the goal of reducing  $PFD_{Avg}$  are given below.

- A novel method to detect "contact weld failure" of Electro Magnetic (EM) relay is proposed which helps in online diagnostics without disturbing the load connected to the relay contact. The method uses the differences in characteristic decay of coil current during de-energization process between a healthy relay and a relay whose contacts got welded. The method works on the principle of de-energizing followed by quick reenergization of relay coil.

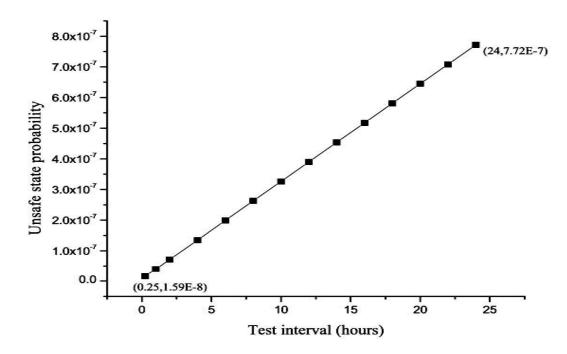

- The practical implementation and verification of relay contact weld detection circuit without any impact on functional circuit is verified with a relay output card. Markov model is developed to demonstrate reduction in unsafe state probability of the system.

The study has been shown that failure probability of each redundant channel can be reduced by ≈ 48 folds with this diagnostic technique.

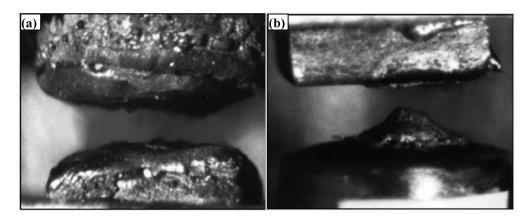

- Reliability demonstration testing as per MIL-HDBK-781A is carried out to confirm the

failure data of EM contactor. Failure analysis of degraded contacts is performed with

SEM (Scanning Electron Microscopy) and EDS (Energy Dispersive Spectroscopy). The

impact of EM contactor failure on uncontrolled withdrawal of neutron absorber rods in

PFBR is analyzed.

• Inherent fail-safe circuits do not require diagnostics since any of the failures in the circuit will automatically lead to a safe state of the final control element. Thus, inherent fail-safe design is studied as an alternative approach to systems with periodic self-testing. A novel inherently fail-safe AND gate is proposed. An inherent fail-safe pulsating electronic logic based valve drive circuit with the AND gate is designed for a decay heat removal system. Quantitative analysis has shown a very low PFD<sub>Avg</sub> since the system fails in unsafe mode only upon combination of multiple failures.

Overall the work has proposed EM relays with online diagnostics and inherently fail-safe circuits to reduce the  $PFD_{Avg}$  of safety systems in a fast reactor.

## LIST OF FIGURES

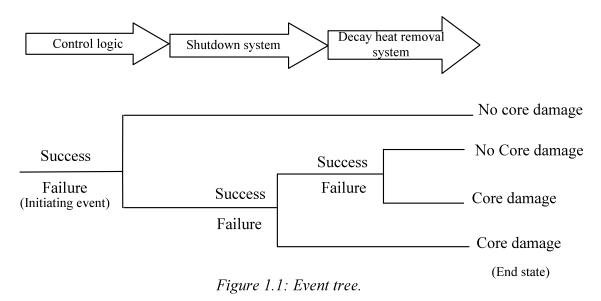

| Figure 1.1: Event tree                                                                  | 2            |

|-----------------------------------------------------------------------------------------|--------------|

| Figure 1.2: Structure of I&C in a NPP [2].                                              | 5            |

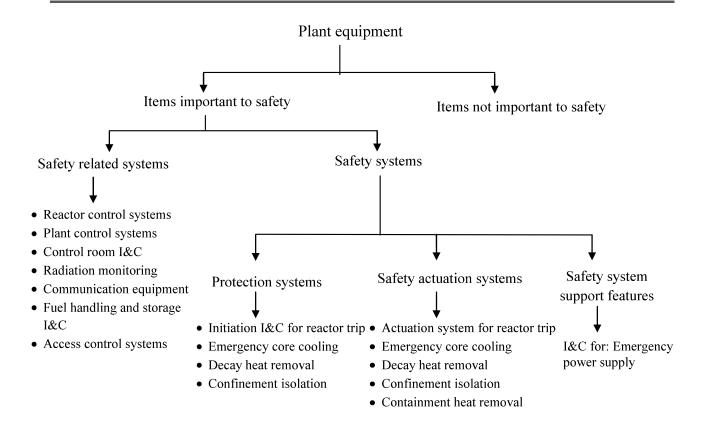

| Figure 1.3: Classification of I&C systems in a NPP                                      | 6            |

| Figure 1.4: Failure rate distribution [5]                                               | 7            |

| Figure 1.5: PFD <sub>Avg</sub> of a periodically proof tested system                    | 8            |

| Figure 1.6: Schematic of shutdown system.                                               | 15           |

| Figure 2.1: Flow sheet of PFBR.                                                         | 23           |

| Figure 2.2: Shutdown system in PFBR                                                     | 25           |

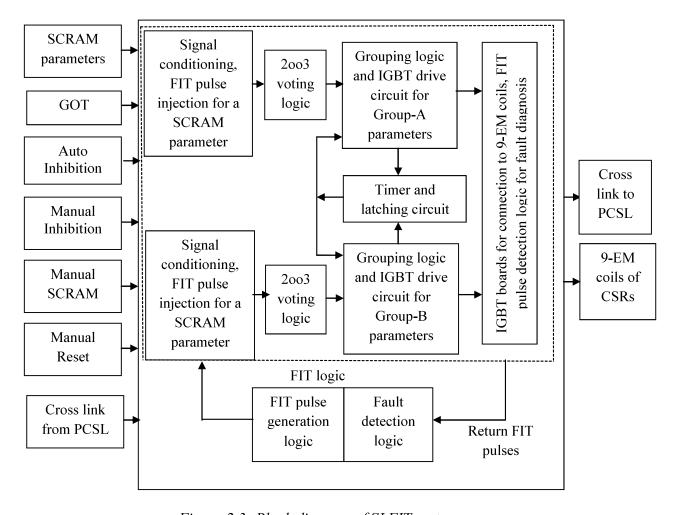

| Figure 2.3: Block diagram of SLFIT system.                                              | 29           |

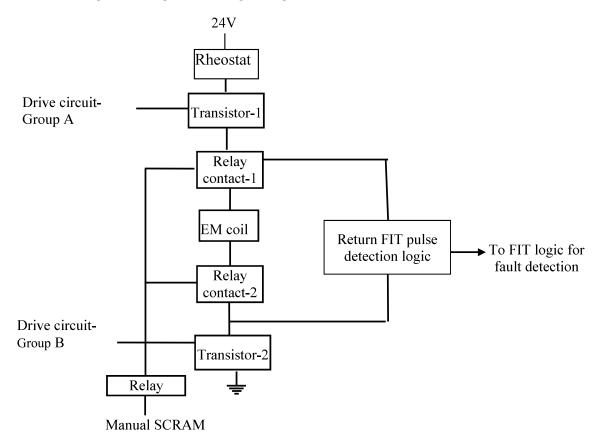

| Figure 2.4: Electromagnet coil connection diagram.                                      | 30           |

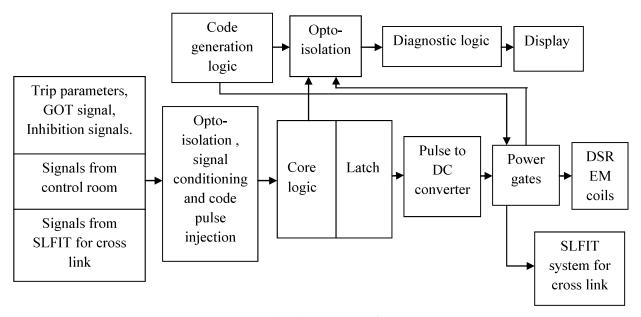

| Figure 2.5: Block diagram of PCSL system.                                               | 32           |

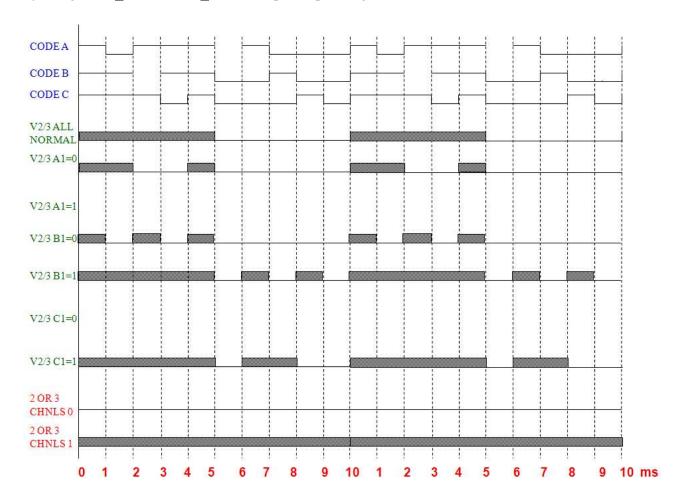

| Figure 2.6: PCSL timing diagram.                                                        | 33           |

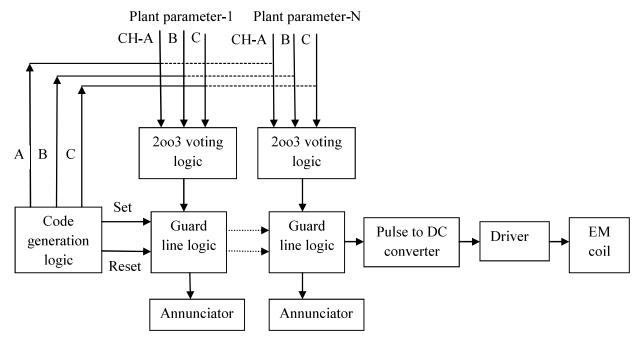

| Figure 2.7: PCSL for multiple parameters.                                               | 34           |

| Figure 2.8: Instrumentation in CSRDM                                                    | 35           |

| Figure 2.9: Block diagram of AIC.                                                       | 40           |

| Figure 2.10: Block diagram of AOC                                                       | 43           |

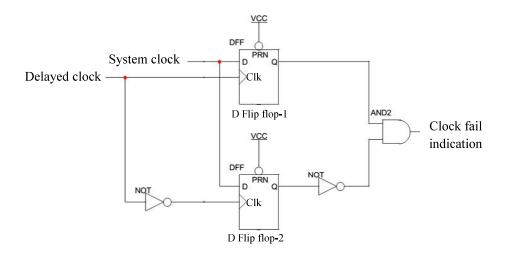

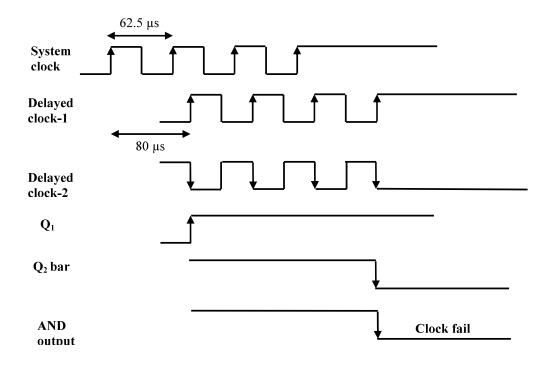

| Figure 2.11: Clock fail detection circuit.                                              | 43           |

| Figure 2.12: Waveforms of clock fail detection circuit.                                 | 44           |

| Figure 2.13: Block diagram of ROC                                                       | 45           |

| Figure 2.14: Block diagram of CPU card.                                                 | 47           |

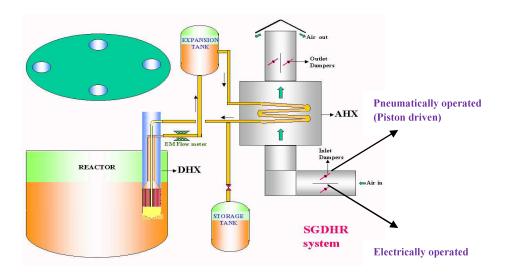

| Figure 2.15: Dampers in SGDHR system.                                                   | 49           |

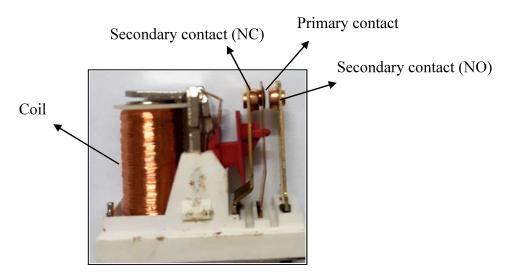

| Figure 3.1: EM relay internal architecture.                                             | 53           |

| Figure 3.2: Contact failure (a) contact material loss due to arc erosion; (b) pip and c | rater        |

| formation [85].                                                                         | 56           |

| Figure 3.3: Application of relay in nuclear power plant shutdown system                 | 59           |

| Figure 3.4: Coil de-energization current decay curve (a)Under healthy contacts; (b)     | Under welded |

| contacts.                                                                               | 61           |

| Figure 3.5: Schematic circuit to implement EM relay diagnostics                         | 63           |

| Figure 3.6: Experimental setup.                                                         | 65           |

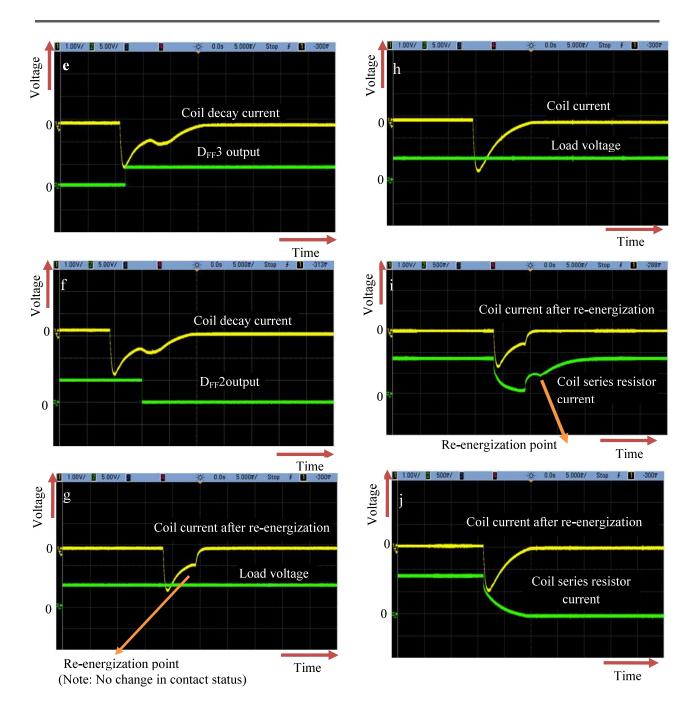

| Figure 3.7: Results of diagnostic circuit.                                              | 66           |

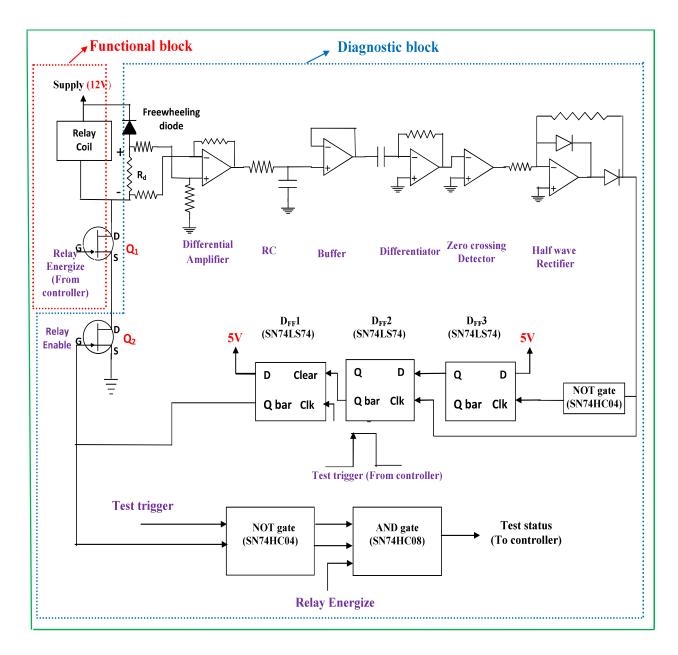

| Figure 4.1: Schematic of relay diagnostic circuitry in ROC                                                       |

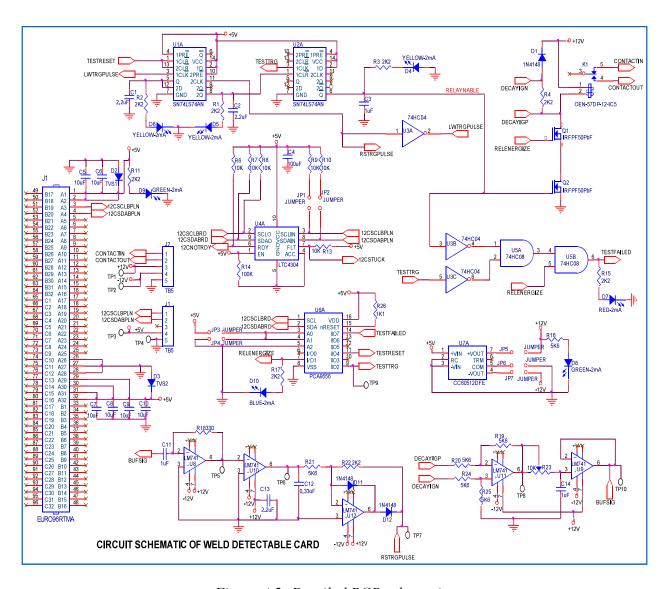

|------------------------------------------------------------------------------------------------------------------|

| Figure 4.2: Detailed PCB schematic. 72                                                                           |

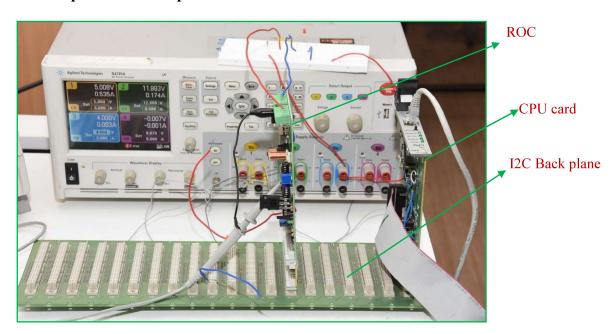

| Figure 4.3: Printed circuit board of ROC                                                                         |

| Figure 4.4: Experimental setup. 74                                                                               |

| Figure 4.5: Markov state space model                                                                             |

| Figure 4.6: Markov state space in ISOGRAPH with state probabilities                                              |

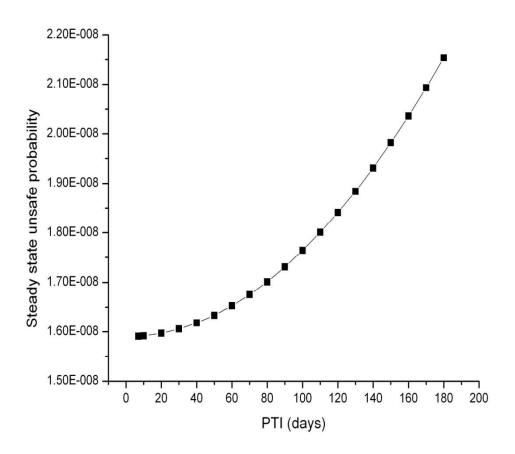

| Figure 4.7: Unsafe state probability variation with test interval                                                |

| Figure 4.8: Unsafe state probability variation with proof test interval                                          |

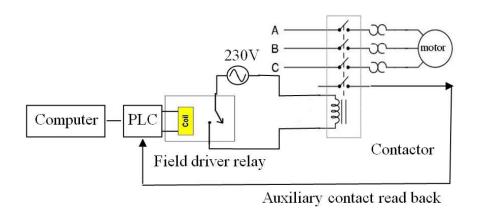

| Figure 5.1: Contactor reliability testing circuit                                                                |

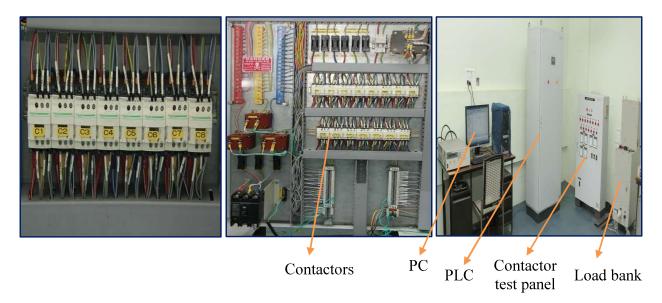

| Figure 5.2: Experimental setup. 95                                                                               |

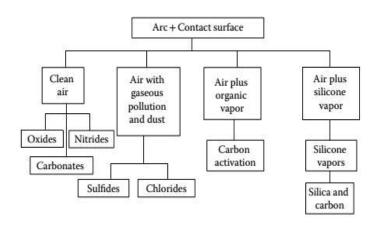

| Figure 5.3: Possible interactions of electric contacts and the ambient air during arcing 97                      |

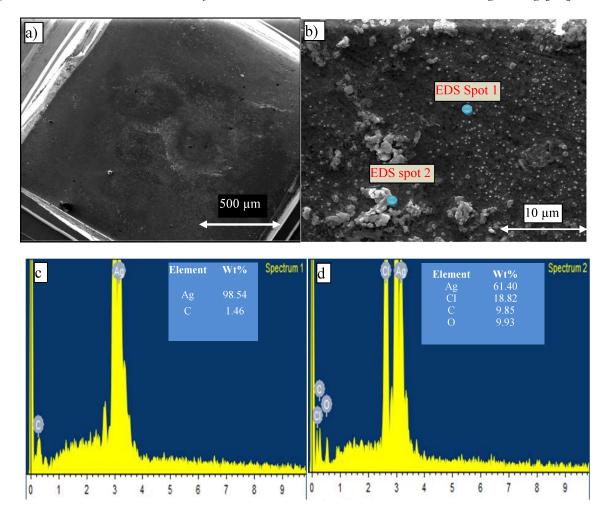

| Figure 5.4: Failure analysis: (a-b) SEM images of failed relay; (c-d) EDS spectrum with                          |

| elemental composition of failed relay with their weight percentages in dark and bright region 97                 |

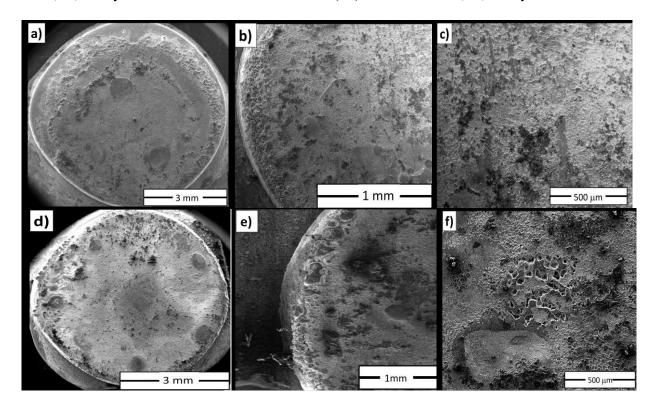

| Figure 5.5: Surface morphology: (a-c) Deformation on C <sub>1</sub> contact; (d-f) Deformation on C <sub>2</sub> |

| contact98                                                                                                        |

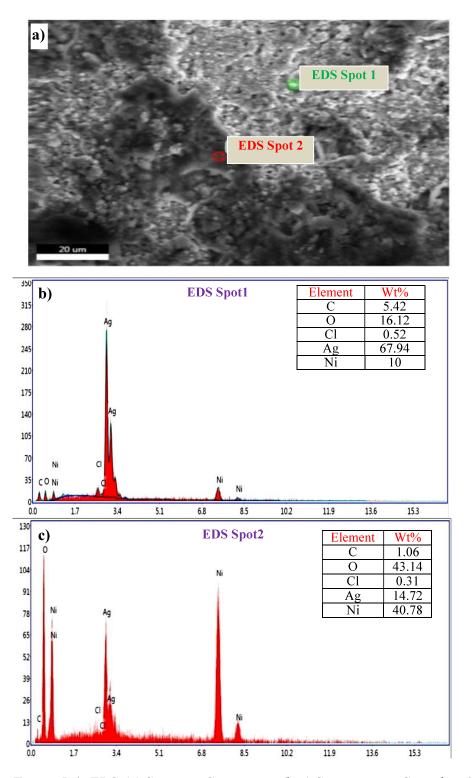

| Figure 5.6: EDS (a) Spots on C <sub>1</sub> contact; (b-c) Spectrum on C <sub>1</sub> with wt%                   |

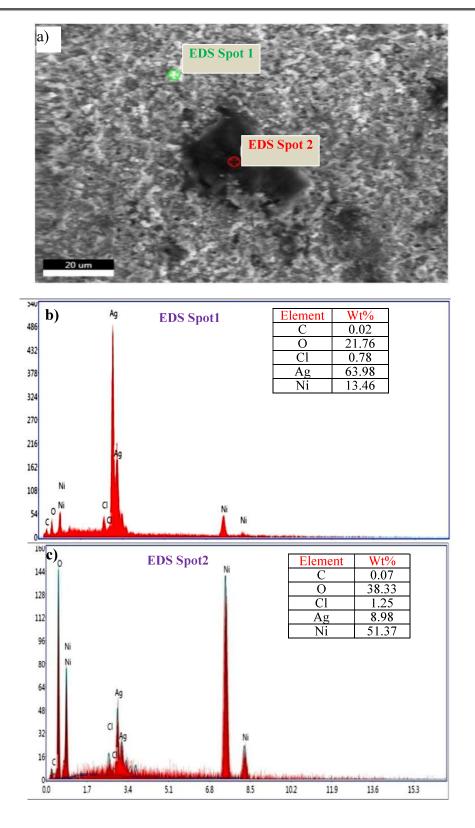

| Figure 5.7: EDS (a) Spots on C <sub>2</sub> contact; (b-c) Spectrum on C <sub>2</sub> with wt%                   |

| Figure 6.1: Fail-safe AND gate (a) Design; (b) Pulse input, pulse transformer output and                         |

| capacitor voltage waveforms; (c) Pulse inputs, capacitor voltage and AND output waveforms.                       |

|                                                                                                                  |

| Figure 6.2: Logic circuit to drive solenoid valves                                                               |

| Figure 6.3: Schematic of fail-safe pulsing circuitry for controlling $V_3$ and $V_4$ valves                      |

| Figure 6.4: Experimental setup. 112                                                                              |

| Figure 6.5: During healthy operation outputs waveforms at different stages (a)Timer                              |

| synchronization pulses; (b)AND gate output; (c)OR gate output; (d)24V pulse transformer                          |

| output, 24V capacitor voltage output                                                                             |

| Figure 6.6: Failure mode effect analysis results.                                                                |

## LIST OF TABLES

| Table 1.1: PFD <sub>Avg</sub> equations for various architectures.                    | 11  |

|---------------------------------------------------------------------------------------|-----|

| Table 1.2: Relation between design technique and PFD <sub>Avg</sub>                   | 12  |

| Table 2.1: Design basis events.                                                       | 23  |

| Table 3.1: Contact failure modes [83].                                                | 54  |

| Table 3.2: Physical effects on contact reliability [83].                              | 54  |

| Table 3.3: Failure modes and root causes [84].                                        | 55  |

| Table 3.4: Test parameters.                                                           | 64  |

| Table 4.1: Notations for Markov model.                                                | 75  |

| Table 4.2: Notations used for functional block status in Markov model                 | 77  |

| Table 4.3: Possible states of the system.                                             | 77  |

| Table 4.4: Failure rate of TI UA-741                                                  | 79  |

| Table 4.5: Failure rate of diagnostic block.                                          | 79  |

| Table 4.6: Parameter values for Markov analysis                                       | 83  |

| Table 4.7: Variation of unsafe state probabilities with diagnostic block failure rate | 87  |

| Table 5.1: Failure ratios of Normally Open contactor as per IEC 60947 [62]            | 90  |

| Table 5.2: Fixed duration test plans [94].                                            | 92  |

| Table 5.3: Contactor specifications.                                                  | 94  |

| Table 6.1: Comparison of logics with unsafe failure probability.                      | 105 |

| Table 6.2: Failure mode effect analysis.                                              | 117 |

## LIST OF ABBREVIATIONS

ADC Analog to Digital Converter

AERB Atomic Energy Regulatory Board

AI Auto Inhibition

AIC Analog Input Card

AOC Analog Output Card

AS Actuation System

CCF Common Cause Failures

CDA Core Disruptive Accident

CDF Core Damage Frequency

CPLD Complex Programmable Logic Device

CPU Central Processing Unit

CSRDM Control and Safety Rod Drive Mechanism

CTMS Core Temperature Monitoring System

DAC Digital to Analog Converter

DBE Design Basis Event

DD Dangerous Detected

DEC Design Extension Condition

DIC Digital Input Card

DSL Design Safety Limit

DSRDM Diverse and Safety Rod Drive Mechanism

DU Dangerous Undetected

EDAC Error Detection and Correction

EDS Energy Dispersive Spectroscopy

EEPROM Electrically Erasable and Programmable Read only Memory

EM Electro Magnetic

EOC End of Conversion

EPROM Electrically Programmable Read Only Memory

FBTR Fast Breeder Test Reactor

FF Flip Flop

FPGA Field Programmable Gate Array

FPU Floating Point Unit

GOT Good Operation Trip

IA Instrumentation Amplifier

I&C Instrumentation and Control

IEC International Electro technical Commission

IGBT Gate Bipolar Transistor

IHX Intermediate Heat exchangers

LED Light Emitting Diode

LED Light Emitting Diode

MI Manual Inhibition

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MRT Mean Repair Time

MTTR Mean Time to Restoration

MUX Multiplexers

NC Normally Closed NO Normally Open

NPP Nuclear Power Plant

OGDHR Operation Grade Decay Heat Removal

PCB Printed Circuit Board

PCSL Pulse coded Safety Logic

PFBR Prototype Fast Breeder Reactor

PFD<sub>Avg</sub> average Probability of Failure on Demand

PFH Probability of dangerous Failure per Hour

PHWR Pressurized Heavy Water Reactor

PLC Programmable Logic Controller

PSA Probabilistic Safety Analysis

RDT Reliability Demonstration Testing

ROC Relay Output Card

RPS Reactor Protection System

r -y reactor year SC Safety Class

SCRAM Safety and Control Rods Accelerated Movement

SDS Shut Down System

SD Safe Detected

SEM Scanning Electron Microscopy

SIS Safety Instrumented System

SGDHR Safety Grade Decay Heat Removal SGE SCRAM Generation Electronics

SLFIT Safety Logic with Finite Impulse Test

SOC Start Of Conversion

SOLC Switch Over Logic Circuit

SPDT Single Pole Double Throw

SRAM Static Random Access Memory

SU Safe Undetected

TIU Test Interface Unit

TTL Transistor Transistor Logic

TMR Triple Modular Redundancy

VME Versa Module Europa

1

## INTRODUCTION

## 1.1 Background

Nuclear power plants (NPPs) are designed to achieve high level of safety at all stages of its lifetime, including extreme natural events like earthquake, flood, tsunami etc. The design has to ensure protection of the workers, public and the environment from the harmful effects of radiations emerging from the plant. To achieve this, the 'defense in depth' philosophy in designing and operating of nuclear facilities which prevents and mitigates accidents, that release radiation or hazardous materials used. The key point is creating multiple independent and redundant layers of defense to compensate for the potential human and mechanical failures so that no single layer, no matter how robust, is exclusively relied upon. Defense in depth includes the use of access controls, physical barriers, redundant and diverse key safety functions, and emergency response measures. The Instrumentation and Control (I&C) system play a key role to ensure the safe and efficient operation of a nuclear plant and they are generally designed on the basis of their function and significance to safety. There are a number of vital functions that must be performed by I&C systems. The important safety functions that are essential to be performed for ensuring safety are (a) control of core reactivity (b) removal of heat from the core and (c) confinement of radioactive materials and control of operational discharges, as well as limitation of accidental releases. A comprehensive safety assessment, using both deterministic and probabilistic safety analysis (PSA) methods, is usually made to ensure that all safety

requirements established for the design are met and are in accordance with relevant national and international codes and standards, laws and regulations.

Figure 1.1 gives a sketch of an event tree of three systems, viz. control logic, shutdown and decay heat removal, and their failure propagation leading to the core damage. A probabilistic risk assessment parameter called the Core Damage Frequency (CDF) is generally used to quantify the probability of a Core Disruptive Accident (CDA). The three systems mentioned above are considered as "safety critical" and are necessary to be highly reliable to achieve a low value of CDF (~10<sup>-6</sup>-10<sup>-7</sup>/r-y) (reactor-year). Control system failure would cause overpower or under-cooling and can be the initiating event which has a potential for core damage in case of multiple failures. However, the failure at this stage will be handled by shutdown systems and decay heat removal systems. A list of shutdown parameters are provided in the design and their thresholds are obtained by carrying out the transient analysis of the Design Basis Events (DBEs) which challenge the Design Safety Limits (DSL) on coolant, clad and fuel. The timely action of shutdown system during any transient ensures safe shutdown such that maximum values of coolant, clad and fuel temperatures reached are limited below the DSL values. Similarly, a combination of active and passive decay heat removal circuits ensure the decay heat removal

without violating the DSL values on coolant, clad and fuel. Further, in addition to defense in depth philosophy, the concept of periodic surveillance and fail-safe design is also employed to obtain the stringent reliability requirement of very low value of CDF. The fail-safe behavior is the capability of any system or a component to reach a predefined safe state in the event of malfunction of component(s). While it would be difficult to reduce the failure probability of I&C systems beyond a lower limit, it would still be possible to reduce the "unsafe" failure probability by invoking fail-safe design. In a NPP, I&C for shutdown systems are to be designed "fail-safe" so that any fault in sensors, logic processors or final control elements will lead to shutdown of the reactor. Similarly, systems for decay heat removal should ensure timely initiation and sustenance of decay heat removal after reactor shutdown. Any fault in such systems should initiate unintended decay heat removal even if it leads to loss of power rather than failure to initiate safety action.

The fail-safe safety systems are necessary to be incorporated in the design of Fast Breeder Reactors (FBRs). Such reactors are recognized for India's second-stage nuclear energy programme, which is aimed at better utilization of its limited Uranium and abundant Thorium. Unlike thermal reactors, fast reactors are designed not in the most reactive configuration. Further, they have smaller core size with high power density. They are also characterized by very low prompt neutron life time  $\sim 10^{-7}$  seconds and low effective delayed neutron fraction ( $\beta_{eff}$ ). Hence, they require a fast acting shutdown system and coolants with high heat transfer capacity. The systems used in PHWRs like poison injection and moderator dumping are not suitable for FBRs. The designs of I&C systems for shutdown, core monitoring and decay heat removal are very challenging in sodium cooled fast reactors because they have to provide high levels of safety. There are many I&C systems working in the sodium environment at high temperatures and high radiation dose. The decay heat removal systems in a pool type FBR are typically

passive in nature depending on natural circulation of sodium with minimal intervention of I&C. Fast reactor technology has been demonstrated in an indigenously developed 40MWt sodium cooled mixed carbide fuelled Fast Breeder Test Reactor (FBTR). A 500MWe mixed oxide Prototype Fast Breeder Reactor (PFBR) with sodium coolant is in the advanced stage of commissioning at Kalpakkam. FBRs with improved safety features are also planned for the future. They have to meet the evolving Gen-IV safety criteria which demands practically eliminating the core destructive accidents by adopting the concept of Design Extension Condition (DEC) [1]. This requirement gives us the motivation for a comprehensive study of fail-safe safety system design and finding the areas requiring improvement for meeting the above design objective. In addition, the incident of uncontrolled withdrawal of one absorber rod in FBTR during criticality in the early periods of its operation also encouraged us to perform this study. The present research work is focused towards developing fail-safe safety systems for applications in future fast reactors with improved safety. A review of the current practices, assumptions and techniques followed in I&C for shutdown and decay heat removal systems of a sodium cooled fast reactor towards achieving a fail-safe design is made in the first part of this thesis with emphasize on the areas of concerns for further improvements. Remaining part gives the works carried out as part of this thesis work.

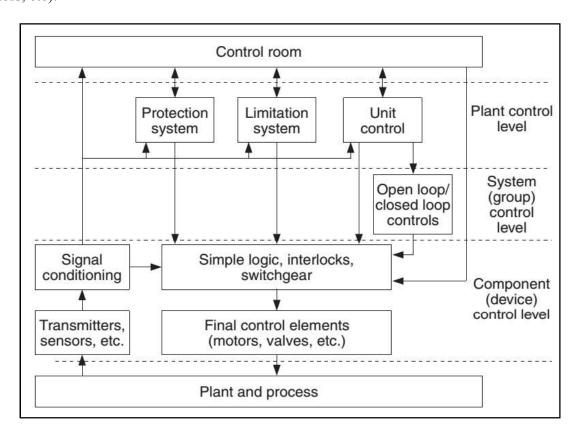

## 1.2 An Overview of Instrumentation and Control Systems in a Nuclear Power Plant

The structure of I&C in a NPP is shown in Figure 1.2. Functions concerning overall plant performance and mode of operation are controlled and monitored at plant control level. The protection systems continuously monitor the state of the reactor and other components, initiating reactor shutdown and maintain it in a safe state during normal and accident conditions. In some NPPs, diverse systems are incorporated to monitor, control and assist in preventing operation

outside the safety margins, which would invoke the safety system. System level keeps all process variables within normal operating values. Component control level is relatively simple logic functions and interlocks, usually in connection with the actuation of single components (pumps, motors, etc).

Figure 1.2: Structure of I&C in a NPP [2].

I&C systems are broadly classified into two systems; systems that perform functions important to safety and systems that perform functions that are not important to safety as shown in Figure 1.3. I&C safety systems perform the primary safety functions such as safe shutdown of the reactor or the removal of residual heat from the core, or they limit the consequences of anticipated operational occurrences and design basis accidents. Safety related I&C systems perform other functions important to safety which is not performed by safety systems.

Figure 1.3: Classification of I&C systems in a NPP.

## 1.3 Fail-safe Design

The design of safety systems should ensure safety of the plant. As per the functional safety standard IEC 61508, released by International Electro-technical Commission, a dangerous failure (unsafe failure) is a failure which has the potential to put the safety system in a hazardous or fail-to-function state. This means that the safety system is not able to respond properly upon a demand. A safe failure is a failure which will not put the safety system in a fail-to-function state. It can rather result in an activation of the safety function without any demand present. A "fail-safe" design has the likelihood that the plant is put in safe state under postulated failures due to engineered design features. Fail-safe design plays an important role in enhancing the safety and achieving probabilistic reliability goals. As a quantitative reliability measure, average Probability of Failure on Demand (PFD $_{Avg}$ ) is used to assess the fail safeness for low demand mode operation [3]. It indicates the probability of a system failing to respond upon a demand in a

specified time interval.  $PFD_{Avg}$ -unsafe, the "failure" means failure in unsafe mode and it is the parameter of interest in safety systems like shutdown systems and decay heat removal systems (Henceforth  $PFD_{Avg}$  is used to refer to  $PFD_{Avg}$ -Unsafe).

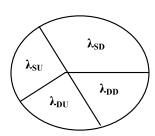

The total failure rate  $\lambda$  of a component is given by  $\lambda = \lambda_D + \lambda_S$  where  $\lambda_D$  and  $\lambda_S$  are respectively the dangerous and safe failure rates [4]. Dangerous failure is a failure which has the potential to put the safety system in a fail-to-function state. This means that the safety system is not able to respond properly upon a demand. A safe failure will result in an activation of the safety function without any demand present. Both dangerous and safe failures can further be split into detected and undetected as shown in Figure 1.4. It implies that a detected failure is revealed at the time the failure arises while an undetected failure discloses when the safety is function tested or sometimes only upon a demand.

$\lambda_{SD}$  = Safe Detected failure rate

$\lambda_{SU}$  = Safe Undetected failure rate

$\lambda_{\rm DD}$  = Dangerous Detected failure rate

$\lambda_{DU}$  = Dangerous Undetected failure rate

Safe failure rate  $(\lambda_S) = \lambda_{SD} + \lambda_{SU}$

Dangerous failure rate  $(\lambda_D) = \lambda_{DD} + \lambda_{DU}$

*Figure 1.4: Failure rate distribution [5].*

The basic equation to calculate  $PFD_{Avg}$  is

$$PFD_{Avg} = \frac{1}{\tau} \int_0^{\tau} 1 - e^{-\lambda_{DU}t} dt \approx \frac{\lambda_{DU}\tau}{2}$$

(1)

For very small values of  $\lambda_{DU}$  and practical value of  $\tau$ .

where t is the mission time of the system;  $(0, \tau)$  is the first proof test interval.

Self-diagnostics helps in detecting dangerous failure. A quantitative parameter to represent self-diagnostics is the diagnostic coverage factor, which is defined as the ratio of number of dangerous failures detected to the total number of dangerous failures in the system. Proof testing

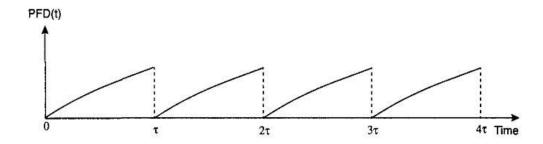

is usually manual and is more elaborative than self-diagnostic tests. Proof test interval ( $\tau$ ) is the interval between subsequent proof tests. Special test points are to be provided in the system to ensure complete fault coverage during a proof test. When the system is assumed to be as-good-as-new after each proof test, variation of PFD with time is shown in Figure 1.5. With the aid of fail-safe design, system can be taken to fail-safe state when dangerous failures are detected. Thus the study of fail-safe design is concerned about related attributes of "high safe to unsafe failure ratio", "higher diagnostic coverage" and "reduced test interval", each contributing to the overall reduction of PFD<sub>Avg</sub>.

Figure 1.5:  $PFD_{Avg}$  of a periodically proof tested system.

## 1.4 Literature Survey

### 1.4.1 Design principles to reduce probability of failure on demand

From the literature survey, it is observed that the following design principles are generally used to achieve very high reliability in safety critical systems.

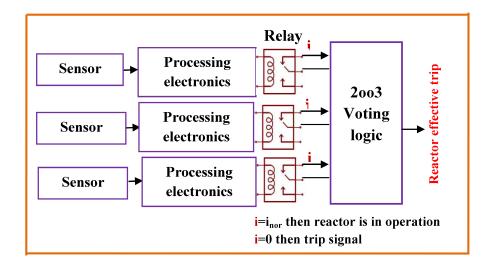

### a. Redundancy and the single failure criterion

The principle of redundancy is applied as a fundamental measure for improving the reliability of systems important to safety. The design ensures that no single failure could result in a loss of the capability of a system to perform its intended safety function [6]. Shutdown systems typically use triple modular redundancy or quadruple redundancy to measure the same process variable [7], [8].

#### b. Diversity

Diverse means are used to gain sufficient protection with respect to dependent failures. Diversity is achieved by technically different functional elements of hardware to implement the same functionality, system software and by using products of different manufacturers [9]. The principle of diversity is applied to enhance reliability and to reduce the potential for common cause failures [6], [10]. Diversity between safety I&C systems and non safety I&C systems is provided for defense in depth against common cause failures [11].

Diverse computerized safety I&C system is also used in reactor protection systems to control the dependent failures [9], [12].

### c. Independence

The principle of independence (functional isolation and physical separation by means of distance, barriers or a special layout for reactor components) is applied to enhance the reliability of systems, in particular with respect to Common Cause Failures (CCF) [6]. In any NPP, at least two shutdown systems are used and these are functionally different and physically separate [13].

### d. Fail-safe design

Systems and components important to safety are designed for fail-safe behavior, as appropriate, so that their failure or the failure of a support feature does not prevent the performance of the intended safety function [14]. For an example, reactor protection systems are designed with passive features to the extent possible and any loss of power to shutdown systems results in drop of rods by gravity, which assures fail-safe shutdown [13], [15].

## e. Periodic surveillance

Safety systems are designed to permit periodic testing of their functionality when the plant is in operation, including the possibility of testing channels independently for the detection of failures and loss of redundancy. Protection system designs have all aspects of functionality testing from the sensor to the final actuator [14]. All systems important to safety include provisions that allow performance of the required testing, including built-in test facilities. These are capable of being checked at regular intervals to ensure continued correct operation [16]. Safety requirements in NPPs have motivated great interest in on-line monitoring technologies and new diagnostic and prognostic methods to anticipate, identify and resolve equipment and process problems and ensure plant safety and efficiency. Hashemian [17] has discussed the on-line monitoring technologies for sensing-line blockages, testing the response time of pressure transmitters, monitoring the pressure transmitters on-line, crosscalibrating temperature sensors, assessing equipment condition, performing predictive maintenance of reactor internals, monitoring fluid flow and extending the life of neutron detectors.

As discussed in section 1.3, PFD<sub>Avg</sub> is the appropriate quantitative parameter for low demand safety instrumented systems. It is of interest to study the mathematical relation between the design principles such as redundancy, diversity, independence, fail-safe design, periodic surveillance and PFD<sub>Avg</sub>. In general, safety instrumented systems employ redundant systems with voting logic. IEC 61508- Part 6 provides a set of simplified expressions for PFD<sub>Avg</sub> to commonly used architectures and is shown in Table 1.1. For example 2003 means 2 out-of 3 voting logic, in which three systems perform a process and that result is processed by a majority voting system to produce a single output & minimum 2 systems should be healthy. In Table 1.1,

- $\beta$  is the fraction of undetected failures that have a common cause and  $\beta_D$  is of those failures that are detected by the diagnostic tests, the fraction that have a common cause.

- Mean Time to Restoration (MTTR) is the time to detect the failure by a diagnostic system and the mean down time until the system is restored.

When a DU fault has been detected during the proof test, Mean Repair Time (MRT) is the associated downtime to repair/restore the system.

| S.No. | Architecture | $\mathrm{PFD}_{\mathrm{Avg}}$                                                                                                                                                                                                                            |

|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | 1001         | $\lambda_D \left( \frac{\lambda_{DU}}{\lambda_D} \left( \frac{\tau}{2} + MRT \right) + \frac{\lambda_{DD}}{\lambda_D} MTTR \right)$                                                                                                                      |

| 2     | 1002         | $2((1-\beta_D)\lambda_{DD} + (1-\beta)\lambda_{DU})^2 \left(\frac{\lambda_{DU}}{\lambda_D} \left(\frac{\tau}{2} + MRT\right) + \frac{\lambda_{DD}}{\lambda_D} MTTR\right) \left(\frac{\lambda_{DU}}{\lambda_D} \left(\frac{\tau}{3} + MRT\right)\right)$ |

|       |              | $+\frac{\lambda_{DD}}{\lambda_{D}}MTTR$                                                                                                                                                                                                                  |

| 3     | 2002         | $2\lambda_D \left( \frac{\lambda_{DU}}{\lambda_D} \left( \frac{\tau}{2} + MRT \right) + \frac{\lambda_{DD}}{\lambda_D} MTTR \right)$                                                                                                                     |

| 4     | 2003         | $6((1-\beta_D)\lambda_{DD} + (1-\beta)\lambda_{DU})^2 \left(\frac{\lambda_{DU}}{\lambda_D} \left(\frac{\tau}{2} + MRT\right) + \frac{\lambda_{DD}}{\lambda_D} MTTR\right) \left(\frac{\lambda_{DU}}{\lambda_D} \left(\frac{\tau}{3} + MRT\right)\right)$ |

|       |              | $+\frac{\lambda_{DD}}{\lambda_{DD}}MTTR + \beta_{D}\lambda_{DD}MTTR + \beta_{D}\lambda_{DU}\left(\frac{\tau}{2} + MRT\right)$                                                                                                                            |

*Table 1.1:*  $PFD_{Avg}$  equations for various architectures.

Several studies have been made on the  $PFD_{Avg}$  formulae of IEC 61508 and the generalized form of koon (k-out-of-n) voting combinations. Jahanian [18] has proposed a generalized  $PFD_{Avg}$  formula for koon architecture and has proven that it matches with IEC 61508 by applying various values to k and n. These expressions assume 100 % proof test coverage. By considering  $PFD_{Avg}$  of voting logic,

$$PFD_{Avg} = \prod\nolimits_{i=1}^{n-k+1} (n-i+1)[(1-\beta)\lambda_{DU} + (1-\beta_D)\lambda_{DD}] \left(\frac{\lambda_{DU}}{\lambda_D} \left(\frac{\tau}{i+1} + MRT\right) + \frac{\lambda_{DD}}{\lambda_D} MTTR\right)$$

$$+\beta\lambda_{DU}\left(\frac{\tau}{2} + MRT\right) + \beta_D\lambda_{DD}MTTR + PFD_{Avg}(voting\ logic)$$

(2)

and

$$PFD_{Avg} \ (voting \ logic) = (\lambda_{1DU} + \lambda_{1DD}) \left[ \frac{\lambda_{1DU}}{\lambda_{1D}} \left( \frac{\tau}{2} + MRT \right) + \frac{\lambda_{1DD}}{\lambda_{1D}} MTTR \right]$$

(3)

Equations (2) and (3) show the generalized  $PFD_{Avg}$  for a redundant safety system with voting logic. As was discussed, safety instrumented system uses various design principles to achieve

high reliability. The way in which these design principles impact  $PFD_{Avg}$  is described in Table 1.2.

Table 1.2: Relation between design technique and  $PFD_{Avg}$ .

| S. No. | Design<br>principle | Relevant Parameter in PFD <sub>Avg</sub>                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Redundancy          | • Coefficient term (n-i+1) and power term to $((1-\beta)\lambda_{DD} + (1-\beta)\lambda_{DU})$ are the predominant factors in PFD <sub>Avg</sub> influenced by the chosen redundancy and type of voting.                                                                                                                                                                                                                                |

|        |                     | • Triple Modular Redundancy (TMR) with 2003 voting is often chosen in reactor safety system since it offers a balance between safety and spurious actions. The TMR architecture also allows for taking one of the three channels for testing without shutting down the plant.                                                                                                                                                           |

| 2      | Independence        | <ul> <li>Independence and diversity leads to reduction in common cause failure fraction. It is apparent from equation I that β and β<sub>D</sub> has a strong potential to nullify the benefits from redundancy.</li> <li>Providing dedicated sensors for redundant channels, independent power supply, placing redundant signal processing electronics in three separate rooms, following different cable routing paths are</li> </ul> |

| 3      | Diversity           | <ul> <li>typical independence features in a NPP safety system.</li> <li>Sensors with diverse working principles, different technologies in signal processing electronics and using different methods for final actuation are typically followed for diversity in a NPP.</li> </ul>                                                                                                                                                      |

| S. No. | Design<br>principle | Relevant Parameter in PFD <sub>Avg</sub>                                                      |

|--------|---------------------|-----------------------------------------------------------------------------------------------|

| 4      | Periodic            | <ul> <li>λ<sub>DU</sub> is reduced by improved diagnostic coverage during periodic</li> </ul> |

| '      |                     |                                                                                               |

|        | surveillance        | self-tests.                                                                                   |

|        |                     | • Effect of $\lambda_{DU}$ on PFD Avg is reduced with frequent proof tests. $\tau$ is         |

|        |                     | typically in days or months.                                                                  |

|        |                     | • Effect of $\lambda_{DD}$ on PFD $_{Avg}$ is reduced by frequent self-tests. In              |

|        |                     | digital I&C systems, test interval can be in seconds or lesser.                               |

|        |                     | Diagnostic coverage is one of the most important design                                       |

|        |                     | parameters to measure the effectiveness of safety protection                                  |

|        |                     | systems. The influence of diagnostic coverage, proof test interval                            |

|        |                     | and common cause failures on $PFD_{Avg}$ is detailed in [19], [20] and                        |

|        |                     | [21]. The shorter proof test period and the higher proof test coverage                        |

|        |                     | indicate the smaller probability of failure on demand. Velten et al.,                         |

|        |                     | [22] have studied the effect of diagnostic coverage, proof test                               |

|        |                     | coverage and proof test interval on PFD <sub>Avg</sub> for different                          |

|        |                     | architectures. The diagnostic coverage and proof test interval have                           |

|        |                     | the most influence on PFD <sub>Avg</sub> for all architectures. Proof test                    |

|        |                     | coverage has less significant effect on $PFD_{Avg}$ .                                         |

| 5      | Fail-safe           | • There are two aspects of fail-safe design. Firstly, $\lambda_D$ is                          |

|        | design              | minimized by appropriate component selection and configuration.                               |

|        |                     | For example, consider in a shutdown system, an electromagnetic                                |

|        |                     | relay is kept energized normally and is de-energized to communicate                           |

|        |                     | a shutdown demand. This configuration depends on the fact that the                            |

| S. No. | Design<br>principle | Relevant Parameter in PFD <sub>Avg</sub>                                                                                                        |

|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                     | failure rate of relays in fail-to-open mode is low compared to fail-to-close mode.                                                              |

|        |                     | The second aspect is to ensure by design that the system is taken  to safe state in case a dengarous failure is detected. This allows for       |

|        |                     | to safe state in case a dangerous failure is detected. This allows for<br>the assumption that all detected failures result in safe state of the |

|        |                     | system in equation 2.                                                                                                                           |

#### 1.4.2 Survey on design principles used in shutdown systems

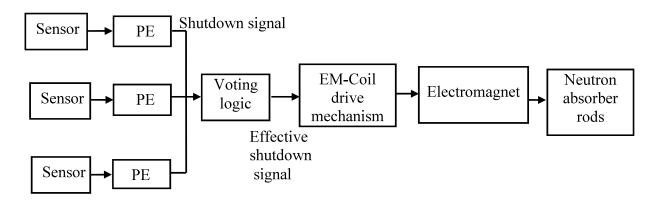

Apart from the design approaches, the general principles used in a typical shutdown system is discussed below. The purpose of the Shutdown System is to terminate the fission reaction upon any anomaly and there by ensure the safety. The three main parts in I&C loop of a shutdown system are sensor, Processing Electronics (PE) and final control element. In a sodium cooled fast reactor, redundant shutdown systems typically employ gravity drop of neutron absorber rods as a means of achieving reliable shutdown. As mentioned earlier, the methods used in Pressurized Heavy Water Reactors (PHWRs) like poison injection and moderator dumping are not suitable or difficult to design in Sodium cooled Fast Reactors. Generalized schematic of SDS is shown in Figure 1.6.

Sensors are used to measure plant parameter like neutron density, coolant temperature, flow rate, etc. All signals are typically measured with redundant and independent sensors. Typically triplicated independent sensors are used to ensure reliability [7]. To diagnose the performance of redundant sensors online, cross calibration method is widely used to detect the drift of any sensor's signal from its redundant group [17], [23]. In this method a simple average is calculated to obtain the band and then existence of each signal inside it is verified. Some other

averaging techniques are band averaging with outliers, weighted average and parity space averaging. Along with cross calibration the various diagnostic methods used in sensor stage are empirical modeling, Kalman filtering, model-based online detection technique using artificial neural networks etc., [24]–[27].

Figure 1.6: Schematic of shutdown system.

Signal processing techniques are applied on redundant sensor signals in Processing Electronics (PE) stage. PE determines whether the process variables are within their allowable band and action is taken to drop the neutron absorber rods into the core when specified conditions are violated. Sensor cable open and cable short can be detected to invalidate sensor readings. Test interface unit is often provided to inject/superimpose the test signals and the measured output parameter is compared with reference input for diagnostic purpose [28].

2003, 2004 are the generally used voting logics to prevent a single failure of the shutdown signal [7], [8], [29], [30]. Highly reliable voting logics are employed in shutdown system [2], [30], [31] since the signals from various PEs are converted into effective shutdown signal by the voting logic.

Computer systems are also used as part of shutdown systems at newly-built and upgraded NPPs. [29], [32]–[36]. For instance, Superpheonix reactor core surveillance with temperature processing using digital system is presented in [37].

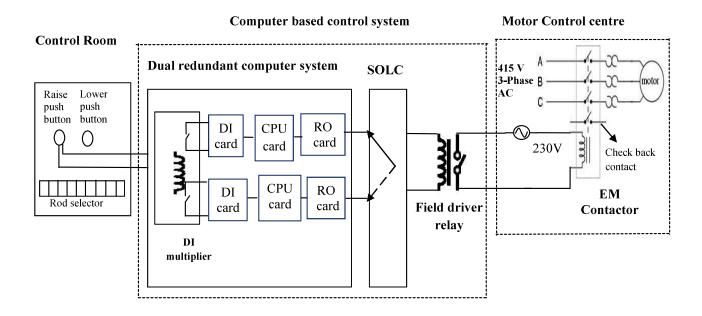

Jia et al., [38] introduces the means to achieve independence in digital I&C system. The typical design measures for electrical isolation are isolation amplifier, control switch, current transformers, optical couplers, relays, circuit breakers etc. The physical separation adopts with barriers, geometry etc. Communication isolation is achieved with different safety channels. CPU is one of the important equipment of computer systems to accord with the single failure criterion and reliability requirement. Li et al., [39] detailed the different redundancy configurations for CPU such as parallel and standby.

To handle large number of field signals in NPP with high reliability and availability, two different backplane bus-based Real Time Computer (RTC) systems with switch over logic system (SOLS) is proposed [12], [40]. Shin et al., [41] have presented the advanced digital reactor protection system with diverse dual processors to prevent common mode failure. The principle of diversity is applied to both hardware design and software design. IAEA-NTR 2008 [42] gives the examples of digital I&C in various NPPs. Computer systems are easily amenable for on-line self-diagnostics [41], [43].

The final control elements are typically electromagnets which hold neutron absorber rods and are dropped into core under gravity when current to electromagnets are terminated. Predominant failures do not affect the safety of the reactor, since the reactor shutdown occurs immediately if the system fails [7], [10], [13], [15], [44]–[48]. Some of the nuclear reactors use self actuated shutdown systems. The design and testing of a simple and reliable self actuated shutdown system is given in [49], [50]. In this system a ferromagnetic Curie temperature permanent magnet holding device is used. Under increased coolant temperature or neutron flux, the magnetic holding force is reduced which leads to gravity drop of neutron absorber rods.

Bartha et al., [51] have presented the testing and diagnostic methodology of triple modular redundant system and proposed the universal test system for functionality test of reactor

shutdown system. Gaubatz [30] has discussed the four divisions of reactor protection system with quad-redundant sensors providing input to four independent microprocessor-based electronics with automated self test and diagnostics.

While general principles are discussed above, evaluation of circuit level details could not be made due to limited published literature on detailed design of reactor circuits. However, a review of various modules used in Prototype Fast Breeder reactor (a 500MWe sodium cooled fast reactor under commissioning in India) is made as part of the present study, which is detailed in Chapter-2. Fail-safe design features are studied in this reactor.

# 1.5 Research Objectives

Based on the literature survey and from the study of safety critical I&C of PFBR,

- i. Fail safeness in absorber rods: Falling under gravity is a natural phenomenon and failure probability to insert the rods is remote. The rods drop under failures like loss of power supply, cable cut and common failures in output circuit.

- ii. The PE and voting logic employs sophisticated electronics or computer systems in which fail-safe design is adequately implemented by using techniques like finite impulse tests, test signal superimposition, discordance monitoring, etc. Very high coverage factor could be achieved due to end to end testing exploiting the simplicity in the functional requirement (the PE is basically a threshold comparator).

- iii. The sensor failures are adequately covered by discordance monitoring (comparison of readings from redundant sensors) and signal validation.

Thus the concept of fail-safe design is well applied in all three sections of the I&C loop namely sensors, PE and final control elements. However, it is observed that there is a generic assumption that EM relays fail open. Electromagnetic (EM) relays are often used to

communicate shutdown signal to voting logic [52]. EM relays are preferred over solid-state relays, IGBT etc due to their favorable failure mode. EM relays predominantly fails in contact fail-to-close mode, which is a safe failure for a design. Hence, relays are kept energized during normal operation and de-energized upon a shutdown demand to achieve a fail-safe behavior. However, literature claims that contact erosion, migration of contact materials, weld etc., are various failure modes due to arcing [53]. Contact welding (fail-to-open) is an unsafe failure mode to be carefully considered for critical application. Short time bounce cause stronger weld due to elastic deformation of the contact material [54], [55]. Morin et al., [56] claims that lamp loads has shown contact weld due to inrush current. Neuhaus et al., [57] stated that configuration of the load circuit determines the actual arc current which influences the weld. Hence it is desirable to detect weld failure in relays

From the literature it is observed that offline diagnostic methods are existing. Fang yao, et al., [58] introduced the dynamic contact resistance measurement as a weld diagnostic parameter. Zhou, et al., [59] shows that DC coil current and contactor current as diagnostic and prognostic parameters for the potential failures of contactors. The pull-in voltage, drop-out voltage and contact resistance are some of the commonly used diagnostic parameters [60]. Coil drive voltage and monitoring the contact with at least  $6V_{DC}$  and 100mA are some of the diagnostic parameters.

Currently, to detect relay failure in NPP systems, periodic opening of EM relay contact in one of the channels in a triple redundant architecture (operating in 2 out of 3 mode) is done Contact status is checked using an auxiliary contact. This is done typically once per shift. If at all an online diagnostic method would exist, this testing could be automated and the test interval time would drastically reduce. *Hence, it is desirable to find a new method to detect weld failure of EM relay contact online (without opening the relay contact)*.

In this thesis work, a technique for online diagnostics of EM relay without affecting the contact status is proposed. The method uses the differences in characteristic decay of coil current during de-energization process between a healthy relay and a relay whose contacts got welded. The method works on the principle of de-energizing followed by quick re-energization of relay coil. The impact of diagnostic circuit on functional circuit is verified by practical implementation of printed circuit board. Further it has been shown in the study that failure probability of each redundant channel can be reduced by around 48 folds by introducing the technique.

As discussed earlier (as shown in Figure 1.1), control system failure contributes probabilistically to CDF by way of increase in demands placed on the shutdown systems. An event took place in FBTR, due to failure in reactor power regulating system. The plant has seen an uncontrolled withdrawal of one of the six absorber rods. Towards approach to criticality, 5 rods were raised to a height of 257mm. The sixth rod was being raised in steps. At about 250mm, even after the release of "raise" push button by the operator, the sixth rod continued to move upward. Investigation has found that this event was due to sluggish behavior of the raise contactor (refusing to open even after the coil supply is withdrawn) which supplied 415V power supply to the motor [61]. As per IEC-60947 [62], for high current relays (contactors), the predominant failure mode is "fail-to-open" (73%). Hence, further studies are required to verify the reliability of EM contactor (weld failure) and its impact on uncontrolled withdrawal of neutron absorber rod.

Reliability Demonstration Testing (RDT) is conducted to electromagnetic contactors as part of this study. The test plan is selected from MIL-HDBK-781A for fixed duration to verify the contactor failure modes. RDT has shown that failure probability of fail-to-open mode is less under the influence of cyclic stress to this particular contactor model. Surface morphology studies have shown formation of Ni precipitates due to arcing.

It is also observed that much of the circuits depend on periodic testing as a powerful defense against unsafe failures. Inherent fail-safe circuits do not require diagnostics since any of the failures in the circuit will automatically lead to a safe state of the final control element. Thus, inherent fail-safe design is a design alternative to systems with periodic self-testing. These circuits will have a lower PFD<sub>Avg</sub> since the periodicity of self-test is tending to zero and the issues arising out of failures in diagnostic circuitry does not exist. However, it would be difficult to have inherently fail-safe design for complicated circuitry. *The potential for using inherently fail-safe circuits are to be explored to achieve very low PFD*<sub>Avg</sub> as an alternative to systems with periodic self-tests.

In this thesis, a novel fail-safe AND gate is proposed and it is experimentally demonstrated as fail-safe under all probable failure modes. An inherent fail-safe pulsating electronic logic valve drive circuit with AND gate is designed for a decay heat removal system. This circuit consists of pulse generators, combinational logic (AND/OR) and driver. Quantitative analysis has shown a very low PFD<sub>Avg</sub> since the system fails in unsafe mode only upon combination of multiple failures.

#### 1.6 Organization of the Thesis

From the above listed objectives, the thesis is structured into seven chapters.

**Chapter 2** elaborates the safety critical I&C systems in PFBR such as shutdown system and decay heat removal system. Subsequently, the various design provisions in these systems to reduce PFD<sub>Avg</sub> are discussed and techniques used in achieving fail-safe design of I&C loop are elaborated.

**Chapter 3** presents a novel method developed as part of this thesis work, to detect electromagnetic relay contact in fail-to-open mode failure without disturbing the load attached to

the contact. This method is online, continuous, automatic and facilitates simultaneous testing of redundant channels. Diagnostic circuit and test results are presented in this chapter.

**Chapter 4** presents the practical implementation and verification of relay contact weld detection circuit as proposed in chapter 3 using a relay output card. Markov modeling is established to verify the reliability improvement achieved with online diagnostics. Sensitivity analysis is presented by varying the test interval and proof test interval.

**Chapter 5** discusses the Reliability Demonstration Testing (RDT) of EM contactor to study the impact of uncontrolled withdrawal of neutron absorber rods. Testing was carried out based on a test plan as per Military handbook: MIL-HDBK-781A for fixed testing time method. The results of SEM (Scanning Electron Microscopy) and EDS (Energy Dispersive Spectroscopy) analysis carried out on contact surface to analyze the failure mode are also discussed.

**Chapter 6** discusses inherently fail-safe electronic logic design to lower PFD<sub>Avg</sub>. A novel inherently fail-safe AND gate is proposed. Inherent fail-safe electronic logic circuit with AND gate is investigated for decay heat removal system damper control logic in PFBR.

**Chapter 7** summarizes the major conclusions drawn from the research work towards fail-safe design of safety critical I&C systems. This chapter also explains the scope for possible improvements of our works in future.

2

# STUDY OF SAFETY CRITICAL I&C SYSTEMS IN PFBR

The present chapter provides a review of safety critical I&C systems in Prototype Fast Breeder Reactor such as shutdown system and decay heat removal system. The various design provisions in these systems to reduce  $PFD_{Avg}$  are discussed and techniques used in achieving fail-safe design of I&C are elaborated.

#### 2.1 Introduction

Prototype Fast Breeder Reactor (PFBR) is a 1250MWt, 500MWe, sodium cooled, Plutonium oxide-Uranium Oxide fuelled, pool type fast reactor under commissioning in India. All reactor structures, systems and components are classified systematically based on their safety functions. The events with a frequency of occurrence ≥10<sup>-6</sup>/year are considered as a Design Basis Event (DBE) and these have been further classified into categories I–IV events as shown in Table 2.1. The DBEs are the set of events that serve as the basis for the establishment of design requirements to systems, structures and components within the plant. DBEs include normal operations, operational transients and certain accident conditions under postulated initiating events considered in the design of the facility.

I&C systems of PFBR are classified as Safety Class (SC)-1 (safety-critical), Safety Class-2 (safety-related) and Non Nuclear Safety (NNS) systems. All systems which monitor shutdown parameters (SCRAM parameters) like coolant outlet temperature, neutronic flux, primary sodium pump speed, reactor inlet temperature are classified as SC-1. Additionally, I&C of Safety Grade

Decay Heat Removal (SGDHR) system and Reactor Containment Isolation Logic are classified as SC-1 systems.

| Category | Frequency (f) (/r-y)    |

|----------|-------------------------|

| 1        | Normal operations       |

| 2        | $f > 10^{-2}$           |

| 3        | $10^{-2} > f > 10^{-4}$ |

| 4        | $10^{-4} > f > 10^{-6}$ |

Table 2.1: Design basis events.

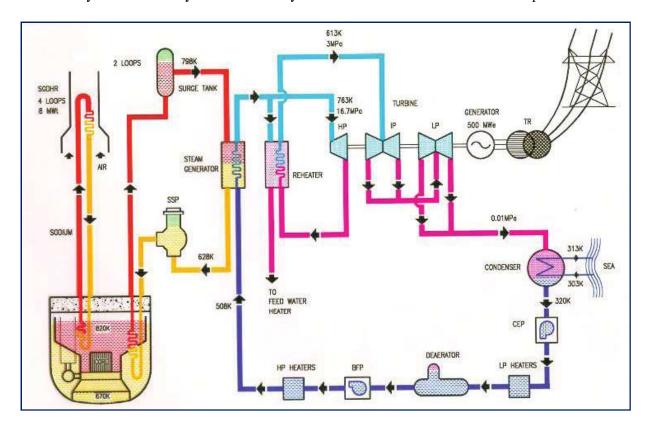

Chetal et al., has detailed the design features of PFBR like reactor core, reactor assembly and I&C [63]. Flow sheet of PFBR is shown in Figure 2.1. Review of shutdown system and decay heat removal system in PFBR is carried out based on [44], [64]–[76] and the internal documents. I&C design details and techniques followed in achieving fail-safe design of shutdown system and decay heat removal system in PFBR are studied in this chapter.

Figure 2.1: Flow sheet of PFBR.

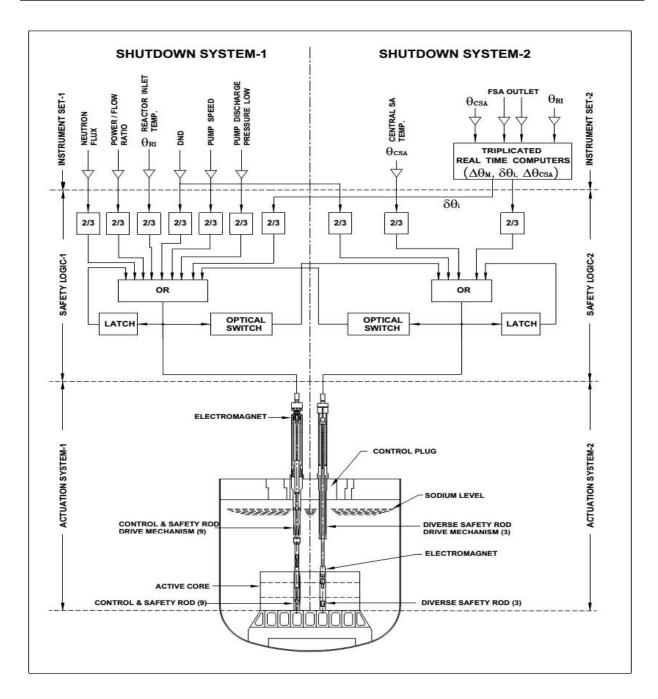

# 2.2 Shutdown System

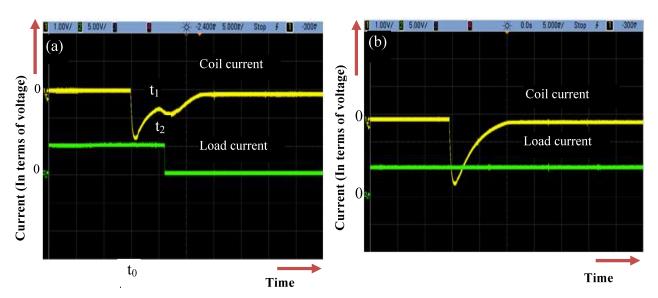

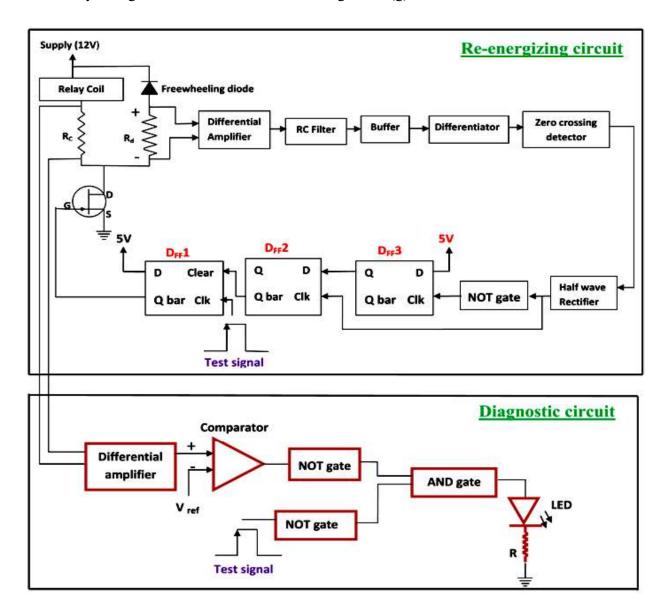

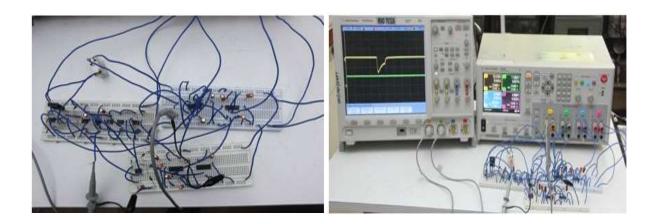

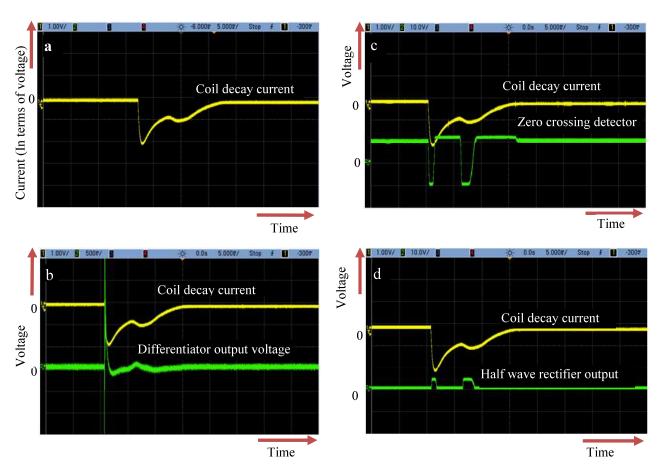

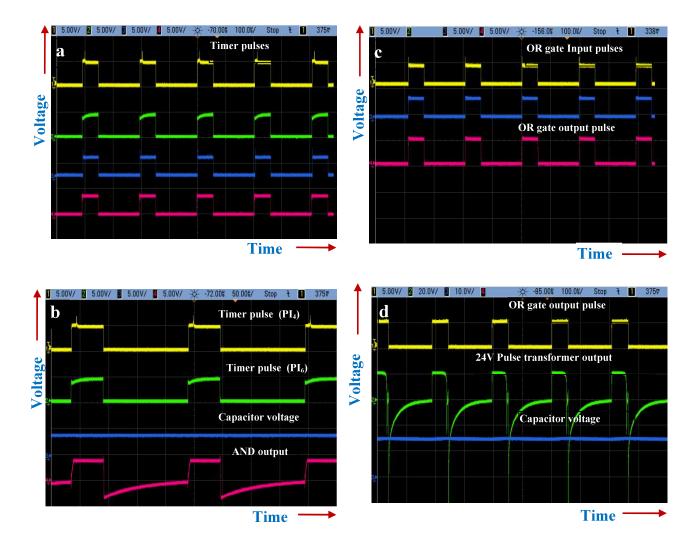

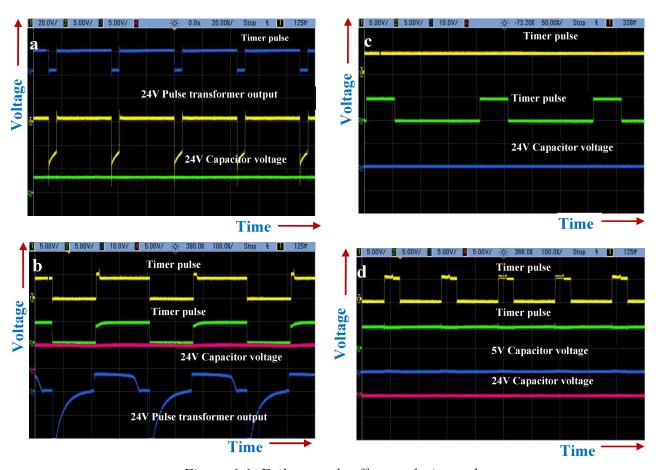

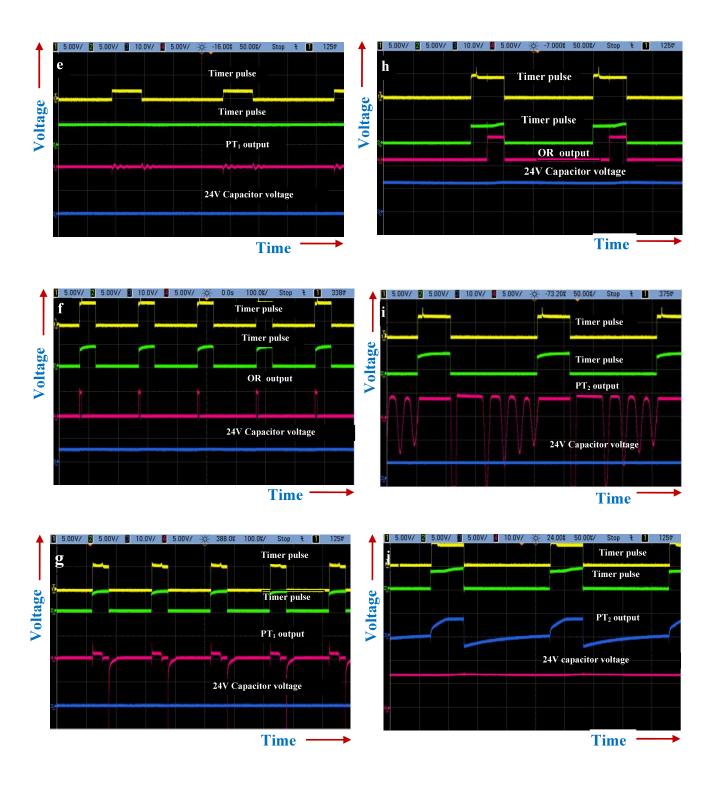

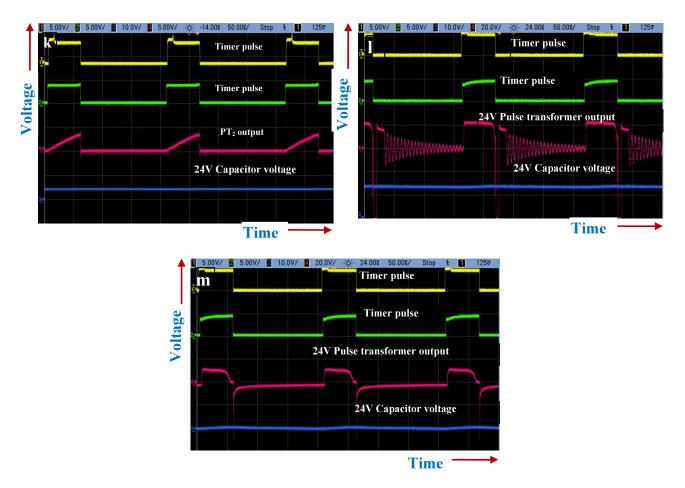

PFBR is provided with two redundant, independent, diverse and fast acting shutdown systems (SDS-1 and SDS-2). The failure probability requirement of each SDS system should be less than 10<sup>-3</sup>. The overall failure probability of SDS should be less than 10<sup>-6</sup> [77].